14 baddr[27:31] signal connections, Table 11-2. baddr connections, 3 register descriptions – Freescale Semiconductor MPC8260 User Manual

Page 430: Table 11-3. 60x bus memory controller registers, Baddr[27:31] signal connections -12, Register descriptions -12, Baddr connections -12, 60x bus memory controller registers -12, Section 11.2.14, “baddr[27:31] signal connections

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

11-12

Freescale Semiconductor

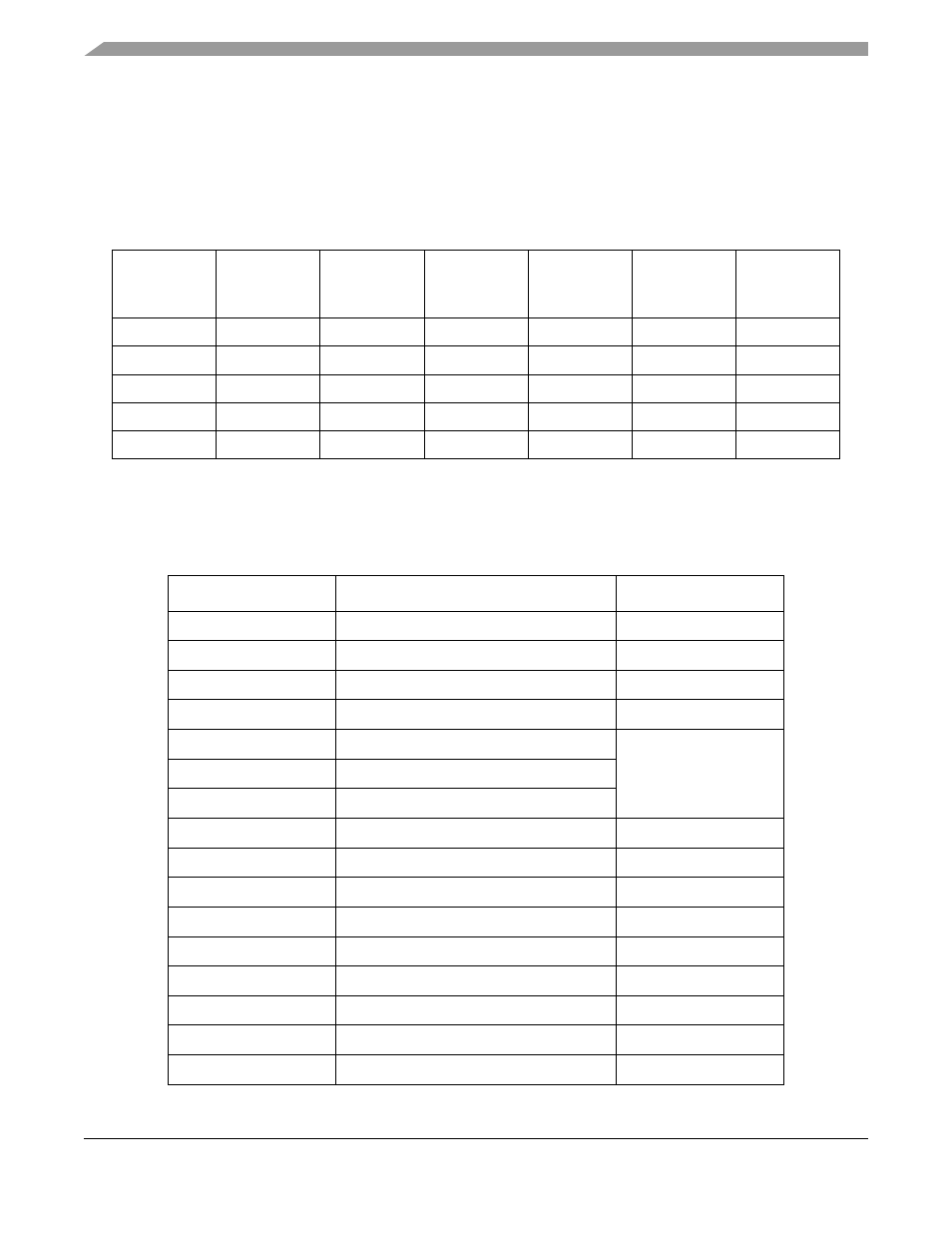

11.2.14 BADDR[27:31] Signal Connections

The memory controller uses BADDR[27:31] to interface memory and peripheral devices on the 60x bus

in 60x-compatible mode. Not all the BADDR line are necessarily used.

Use

to determine which BADDR lines are needed for the device connection.

11.3

Register Descriptions

lists registers used to control the 60x bus memory controller.

Table 11-2. BADDR Connections

BADDR[x]

64/72-Bit Port

Size SDRAM

Non-SDRAM

64-/72-Bit Port

Size Device

32-Bit Port

Size SDRAM

Non-SDRAM

32-Bit Port

Size Device

Any 16-Bit

Port Size

Device

Any 8-Bit Port

Size Device

BADDR[27]

N.C. Connected

N.C. Connected

Connected

Connected

BADDR[28]

N.C. Connected

N.C. Connected

Connected

Connected

BADDR[29]

N.C. N.C N.C. Connected

Connected

Connected

BADDR[30]

N.C. N.C N.C. N.C Connected

Connected

BADDR[31]

N.C. N.C N.C. N.C. N.C. Connected

Table 11-3. 60x Bus Memory Controller Registers

Abbreviation

Name

Reference

BR0–BR11

Base register banks 0–11

Section 11.3.1

OR0–OR11]

Option register banks 0–11

Section 11.3.2

PSDMR

60x bus SDRAM machine mode register

Section 11.3.3

LSDMR

Local bus SDRAM machine mode register

Section 11.3.4

MAMR

UPMA mode register

Section 11.3.5

MBMR

UPMB mode register

MCMR

UPMC mode register

MDR

Memory data register

Section 11.3.6

MAR

Memory address register

Section 11.3.7

MPTPR

Memory refresh timer prescaler register

Section 11.3.12

PURT

60x bus assigned UPM refresh timer

Section 11.3.8

PSRT

60x bus assigned SDRAM refresh timer

Section 11.3.10

LURT

Local bus assigned UPM refresh timer

Section 11.3.9

LSRT

Local bus assigned SDRAM refresh timer

Section 11.3.11

TESCRx

60x bus error status and control registers

Section 11.3.13

LTESCRx

Local bus error status and control regs

Section 11.3.14