12 idma programming examples, Idma programming examples -30, Parallel i/o register programming—port a -30 – Freescale Semiconductor MPC8260 User Manual

Page 674: Parallel i/o register programming—port d -30, Example: peripheral-to-memory mode—idma2 -30, Table 19-13, Table 19-14

SDMA Channels and IDMA Emulation

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

19-30

Freescale Semiconductor

describes parallel I/O register programming for port D (optional).

19.12 IDMA Programming Examples

These programming examples demonstrate the use of most of the different modes and configurations of

the IDMA channels.

19.12.1 Peripheral-to-Memory Mode (60x Bus to Local

Bus)—IDMA2

, the IDMA2 channel reads 8 bytes per DREQ assertion from a fixed address

peripheral located on the 60x bus into the internal buffer. When there is enough data in the internal buffer,

it writes one burst to the memory located on the local bus. The internal buffer size is set to 64 bytes to

handle maximum transfer of a single burst. The IDMA2 channel asserts DONE on the last read transfer of

the last BD to notify the peripheral that there is no data left to transfer.

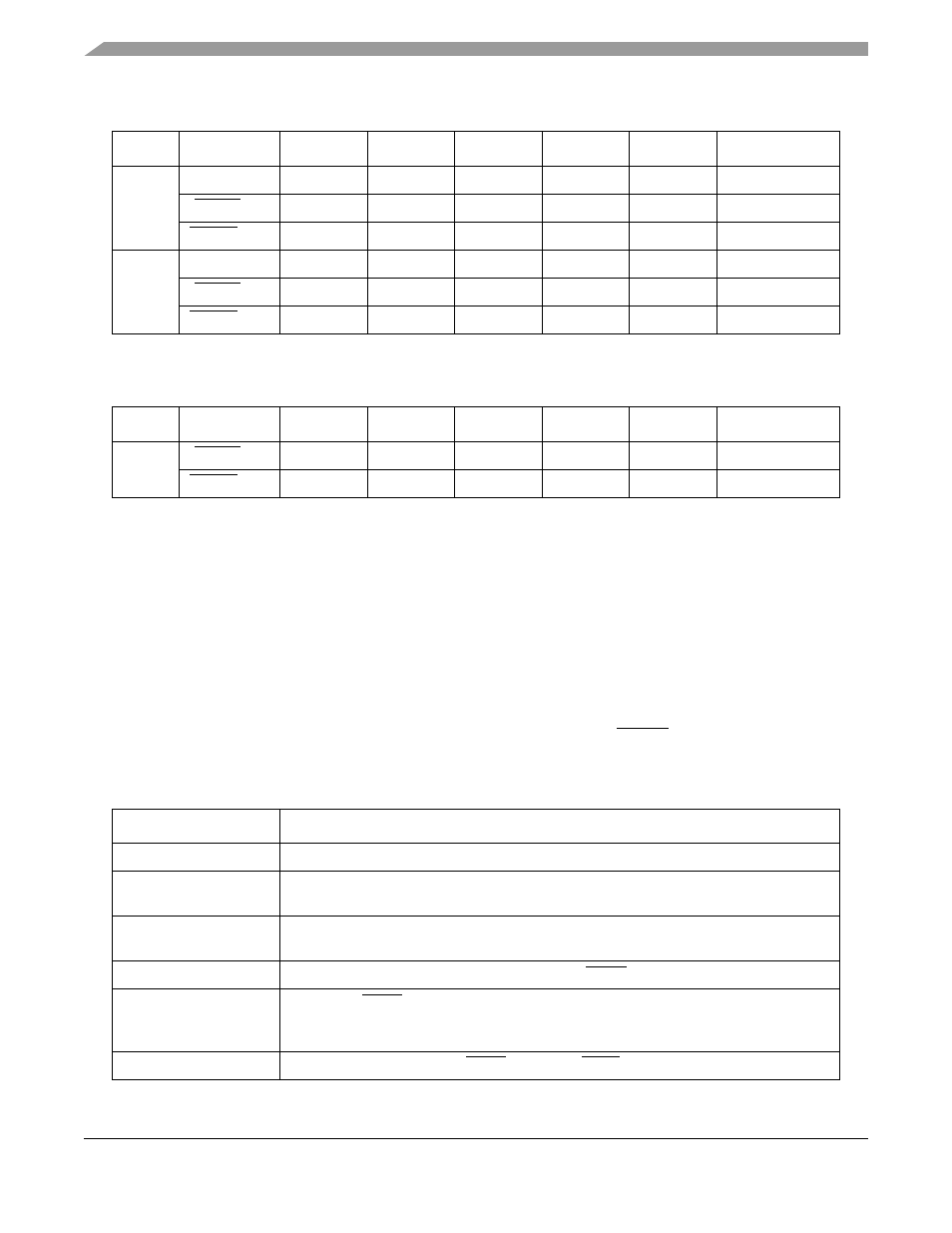

Table 19-13. Parallel I/O Register Programming—Port A

Channel

Signal

Pin

PPARA

PDIRA

PODRA

PSORA

Default

IDMA3

DREQ3 (I)

PA[0]

1

0

0

1

GND

DACK3 (O)

PA[2]

1

1

0

1

—

DONE3 (I/O)

PA[1]

1

0

1

1

VDD

IDMA4

DREQ4 (I)

PA[5]

1

0

0

1

GND

DACK4 (O)

PA[3]

1

1

0

1

—

DONE4 (I/O)

PA[4]

1

0

1

1

VDD

Table 19-14. Parallel I/O Register Programming—Port D

Channel

Signal

Pin

PPARD

PDIRD

PODRD

PSORD

Default

IDMA1

DACK1 (O)

PD[6]

1

1

0

1

—

DONE1 (I/O)

PD[5]

1

0

1

1

VDD

Table 19-15. Example: Peripheral-to-Memory Mode—IDMA2

Important Init Values

Description

DCM(FB) = 0

Not in fly-by mode.

DCM(LP) = 0

Transfers to memory have middle CPM request priority. The destination bus is not

overloaded.

DCM(DMA_WRAP) =

000

The internal buffer is 64 bytes long to support 32-byte transfers to memory on the

destination bus (one 60x burst) on steady-state of work.

DCM(ERM) = 1

Transfers from peripheral are initiated by DREQ. DONE assertion is supported.

DCM(DT) = 0

Assertion of DONE by the peripheral causes the transfer to be terminated, after writing all

the data in the internal buffer to memory, interrupt EDN is set to the core, IDMA channel is

stopped. additional DREQ assertions are ignored, until

START

_

IDMA

command is issued.

DCM(S/D) = 10

Peripheral-to-memory mode. DONE DREQ and DACK are connected to the peripheral.