6 inbound message interrupt mask register (imimr), Table 9-63. imimr field descriptions (continued), Imimr field descriptions -82 – Freescale Semiconductor MPC8260 User Manual

Page 388: Table 9-63 describes imimr fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-82

Freescale Semiconductor

9.12.3.4.6

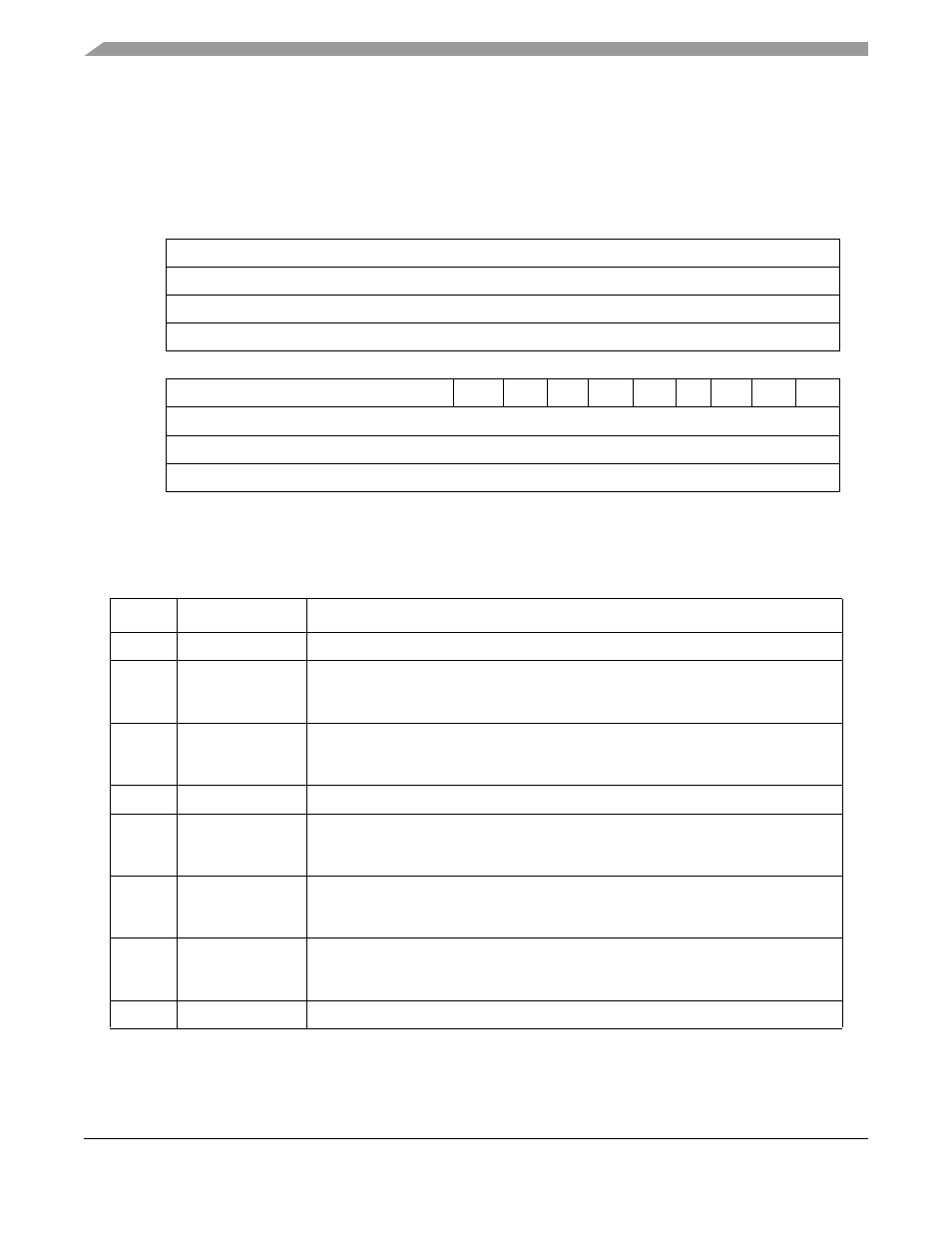

Inbound Message Interrupt Mask Register (IMIMR)

This register contains the interrupt mask of the I

2

O, door bell, and message register events generated by

the PCI master. IMIMR should be accessed only from the 60x bus and only in agent mode. Accesses while

in host mode or from the PCI bus have undefined results.

Figure 9-78. Inbound Message Interrupt Mask Register (IMIMR)

describes IMIMR fields.

31

16

Field

—

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10486

15

9

8

7

6

5

4

3

2

1

0

Field

—

OFOIM IPOIM

—

IPQIM MCIM IDIM

—

IM1IM IM0IM

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10484

Table 9-63. IMIMR Field Descriptions

Bits

Name

Description

31–9

—

Reserved, should be cleared.

8

OFOIM

Outbound free overflow interrupt mask

0 Outbound free overflow interrupt is allowed.

1 Outbound free overflow interrupt is masked.

7

IPOIM

Inbound post overflow interrupt mask

0 Inbound post overflow interrupt is allowed.

1 Inbound post overflow interrupt is masked.

6

—

Reserved, should be cleared.

5

IPQIM

Inbound post queue interrupt mask

0 Inbound post queue interrupt is allowed.

1 Inbound post queue interrupt is masked.

4

MCIM

Machine check interrupt mask

0 Machine check interrupt from the inbound doorbell register is allowed.

1 Machine check interrupt is masked.

3

IDIM

Inbound doorbell interrupt mask

0 Inbound doorbell interrupt is allowed.

1 Inbound doorbell interrupt is masked.

2

—

Reserved, should be cleared.