10 hunt mode (receiver), Table 21-5. toseq field descriptions (continued), Hunt mode (receiver) -9 – Freescale Semiconductor MPC8260 User Manual

Page 713: Transmit out-of-sequence register (toseq) -9, Toseq field descriptions -9

SCC UART Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

21-9

21.10 Hunt Mode (Receiver)

A UART receiver in hunt mode remains deactivated until an idle or address character is recognized,

depending on PSMR[UM]. A receiver is forced into hunt mode by issuing an

ENTER

HUNT

MODE

command.

The receiver aborts any message in progress when

ENTER

HUNT

MODE

is issued. When the message is

finished, the receiver is reenabled by detecting the idle line (one idle character) or by the address bit of the

next message, depending on PSMR[UM]. When a receiver in hunt mode receives a break sequence, it

increments BRKEC and generates a BRK interrupt condition.

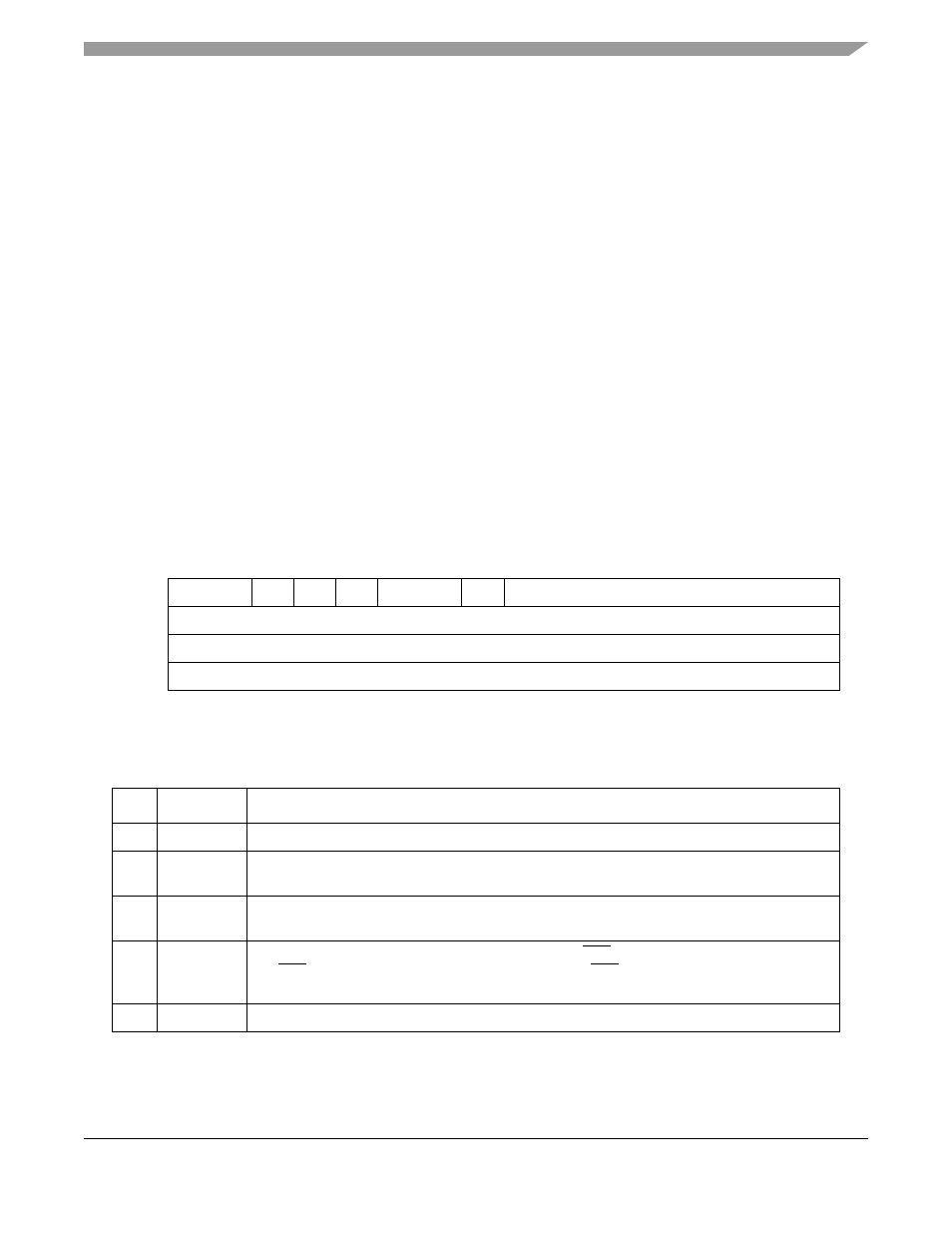

21.11 Inserting Control Characters into the Transmit Data Stream

The SCC UART transmitter can send out-of-sequence, flow-control characters like XON and XOFF. The

controller polls the transmit out-of-sequence register (TOSEQ), shown in

, whenever the

transmitter is enabled for UART operation, including during a UART freeze operation, UART buffer

transmission, and when no buffer is ready for transmission. The TOSEQ character (in CHARSEND) is

sent at a higher priority than the other characters in the transmit buffer, but does not preempt characters

already in the transmit FIFO. This means that the XON or XOFF character may not be sent for eight or

four (SCC) character times. To reduce this latency, set GSMR_H[TFL] to decrease the FIFO size to one

character before enabling the transmitter.

describes TOSEQ fields.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

—

REA

I

CT

—

A

CHARSEND

Reset

0000_0000_0000_0000

R/W

R/W

Addr

SCC base + 0x4E

Figure 21-4. Transmit Out-of-Sequence Register (TOSEQ)

Table 21-5. TOSEQ Field Descriptions

Bit

Name

Description

0–1

—

Reserved, should be cleared.

2

REA

Ready. Set when the character is ready for transmission. Remains 1 while the character is being

sent. The CP clears this bit after transmission.

3

I

Interrupt. If this bit is set, transmission completion is flagged in the event register (SCCE[TX] is

set), triggering a maskable interrupt to the core.

4

CT

Clear-to-send lost. Operates only if the SCC monitors CTS (GSMR_L[DIAG]). The CP sets this

bit if CTS negates when the TOSEQ character is sent. If CTS negates and the TOSEQ character

is sent during a buffer transmission, the TxBD[CT] status bit is also set.

5–6

—

Reserved, should be cleared.