6 extended hold time on read accesses, 5 upm dram configuration example, Extended hold time on read accesses -79 – Freescale Semiconductor MPC8260 User Manual

Page 497: Upm dram configuration example -79, Section 11.6.5, “upm dram configuration example, Figure 11-66

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

11-79

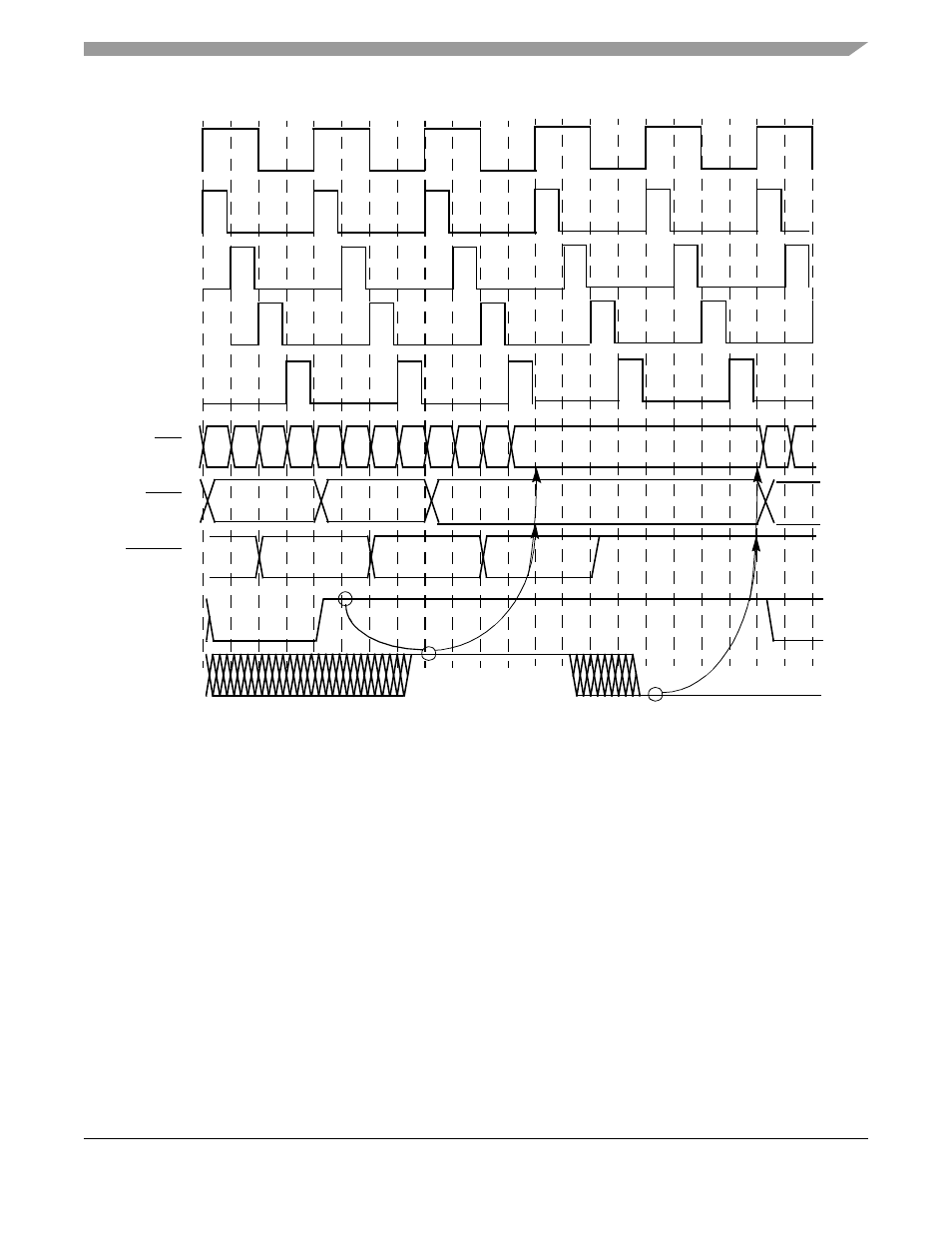

Figure 11-66. Wait Mechanism Timing for Internal and External Synchronous Masters

11.6.4.6

Extended Hold Time on Read Accesses

Slow memory devices that take a long time to turn off their data bus drivers on read accesses should chose

some combination of ORx[EHTR]. Accesses after a read access to the slower memory bank is delayed by

the number of clock cycles specified by

Section 11.5.1.6, “Extended Hold

provides additional information.

11.6.5

UPM DRAM Configuration Example

Consider the following DRAM organization:

•

Eight 64Mbit devices, each organized as 8M x 8bits

•

Each device has 12 row lines and 9 column lines.

CSx

GPL1

WAEN

Word n

Word n+1

c1

c2

c3

c4

c5

c6

c7

c8

UPMWAIT

c9 c10 c11

c12

c13 c14

Word n+2

Wait

Wait

Word n+3

PSDVAL

CLKIN

T1

T2

T3

T4

A

B

C

D