3 fcc protocol-specific mode registers (fpsmrx), Fcc protocol-specific mode registers (fpsmrx) -7, 3 fcc protocol-specific mode registers (fpsmr x) – Freescale Semiconductor MPC8260 User Manual

Page 905

Fast Communications Controllers (FCCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

29-7

NOTE

In addition to selecting the correct mode of operation in GFMRx[MODE],

the user must issue the appropriate CP command and choose the correct

protocol in CPCR (refer to

Section 14.4.1, “CP Command Register

).

29.3

FCC Protocol-Specific Mode Registers (FPSMR

x)

The functionality of the FCC varies according to the protocol selected by GFMR[MODE]. Each FCC has

an additional 32-bit, memory-mapped, read/write protocol-specific mode register (FPSMR) that

configures them specifically for a chosen mode. The section for each specific protocol describes the

FPSMR bits.

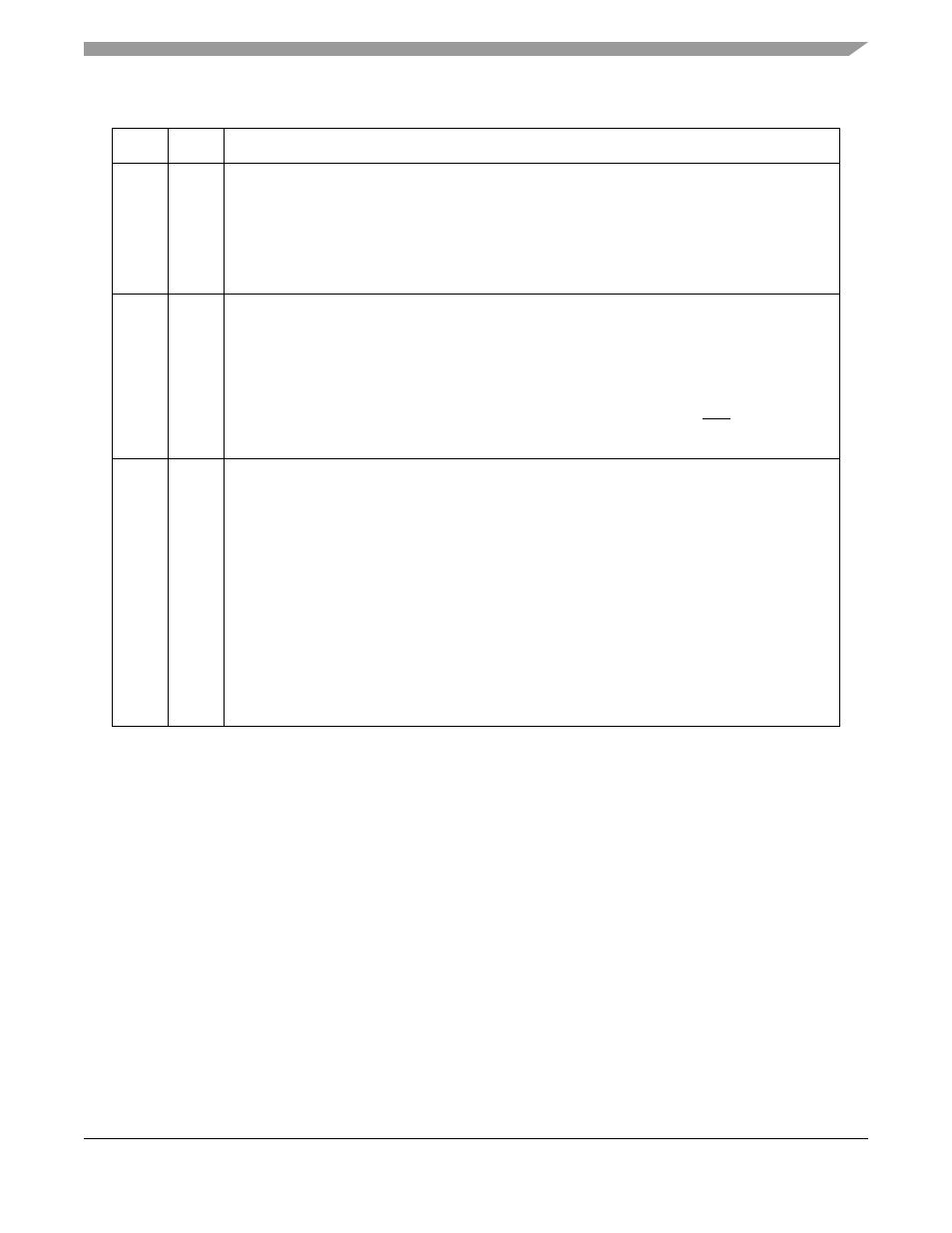

26

ENR

Enable receive. Enables the receiver hardware state machine for this FCC.

0 The receiver is disabled and any data in the receive FIFO buffer is lost. If ENR is cleared during

reception, the receiver aborts the current character.

1 The receiver is enabled.

ENR may be set or cleared regardless of whether serial clocks are present. Describes how to

disable and reenable an FCC. Note that the FCC provides other tools for controlling reception—the

ENTER

HUNT

MODE

command,

CLOSE

RXBD

command, and RxBD[E].

27

ENT

Enable transmit. Enables the transmitter hardware state machine for this FCC.

0 The transmitter is disabled. If ENT is cleared during transmission, the transmitter aborts the

current character and TXD returns to idle state. Data in the transmit shift register is not sent.

1 The transmitter is enabled.

ENT can be set or cleared, regardless of whether serial clocks are present. See

“Disabling the FCCs On-the-Fly

,” for a description of the proper methods to disable and reenable an

FCC. Note that the FCC provides other tools for controlling transmission besides the ENT bit—the

STOP

TRANSMIT

,

GRACEFUL

STOP

TRANSMIT

, and

RESTART

TRANSMIT

commands, CTS flow control, and

TxBD[R].

28–31

MODE Channel protocol mode

0000 HDLC

0001 Reserved for RAM microcode

0010 Reserved

0011 Reserved for RAM microcode

0100 Reserved

0101 Reserved for RAM microcode

0110 Reserved

0111 Reserved for RAM microcode

1000 Reserved

1001 Reserved for RAM microcode

1010 ATM

1011 Reserved for RAM microcode

1100 Ethernet

11xx Reserved

Table 29-2. GFMR Register Field Descriptions (continued)

Bits

Name Description