8 hdlc mode register (psmr), Figure 22-3. hdlc mode register (psmr), Hdlc mode register (psmr) -7 – Freescale Semiconductor MPC8260 User Manual

Page 735: Psmr hdlc field descriptions -7

SCC HDLC Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

22-7

22.8

HDLC Mode Register (PSMR)

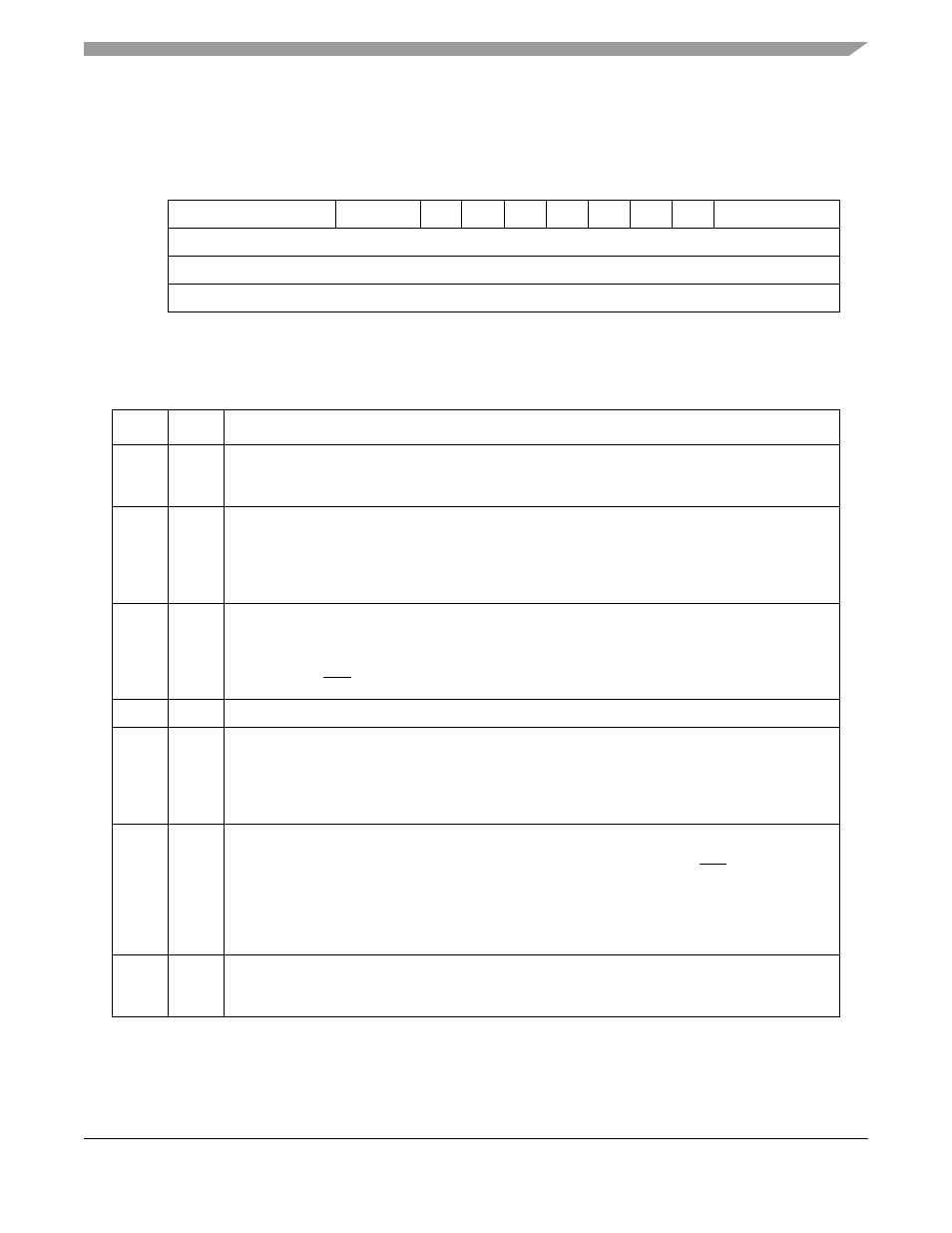

The protocol-specific mode register (PSMR), shown in

, functions as the HDLC mode register.

describes PSMR HDLC fields.

0

3

4

5

6

7

8

9

10

11

12

13

15

Field

NOF

CRC

RTE

—

FSE

DRT

BUS BRM MFF

—

Reset

0

R/W

R/W

Addr

0x0x11A08 (PSMR1); 0x0x11A28 (PSMR2); 0x0x11A48 (PSMR3); 0x0x11A68 (PSMR4)

Figure 22-3. HDLC Mode Register (PSMR)

Table 22-6. PSMR HDLC Field Descriptions

Bits

Name

Description

0-3

NOF

Number of flags. Minimum number of flags between or before frames. If NOF = 0b0000, no flags are

inserted between frames and the closing flag of one frame is followed by the opening flag of the next

frame in the case of back-to-back frames. NOF can be modified on-the-fly.

4–5

CRC

CRC selection.

00 16-bit CCITT-CRC (HDLC). X16 + X12 + X5 + 1.

x1 Reserved.

10 32-bit CCITT-CRC (Ethernet and HDLC). X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 +

X8 + X7 + X5 + X4 + X2 + X1 +1.

6

RTE

Retransmit enable.

0 No retransmission.

1 Automatic frame retransmission is enabled. Particularly useful in the HDLC bus protocol and

ISDN applications where multiple HDLC controllers can collide. Note that retransmission occurs

only if a lost CTS occurs on the first or second buffer of the frame.

7

—

Reserved, should be cleared.

8

FSE

Flag sharing enable. FSE can be set only if GSMR_H[RTSM] is already set. Can be modified

on-the-fly.

0 Normal operation.

1 If NOF[0–3] = 0b0000, a single shared flag is sent between back-to-back frames. Other values of

NOF[0–3] are decremented by 1. Useful in signaling system #7 applications.

9

DRT

Disable receiver while transmitting.

0 Normal operation.

1 As the SCC sends data, the receiver is disabled and gated by the internal RTS. This helps if the

HDLC channel is on a multidrop line and the SCC does not need to receive its own transmission.

Note: If DRT = 1, GSMR_H[CDS] should be cleared unless both of the following are true: the same

clock is used for TCLK and RCLK, and CTS either has synchronous timing or is always

asserted.

10

BUS

HDLC bus mode.

0 Normal HDLC operation.

1 HDLC bus operation is selected. See