Freescale Semiconductor MPC8260 User Manual

Page 231

Reset

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

5-9

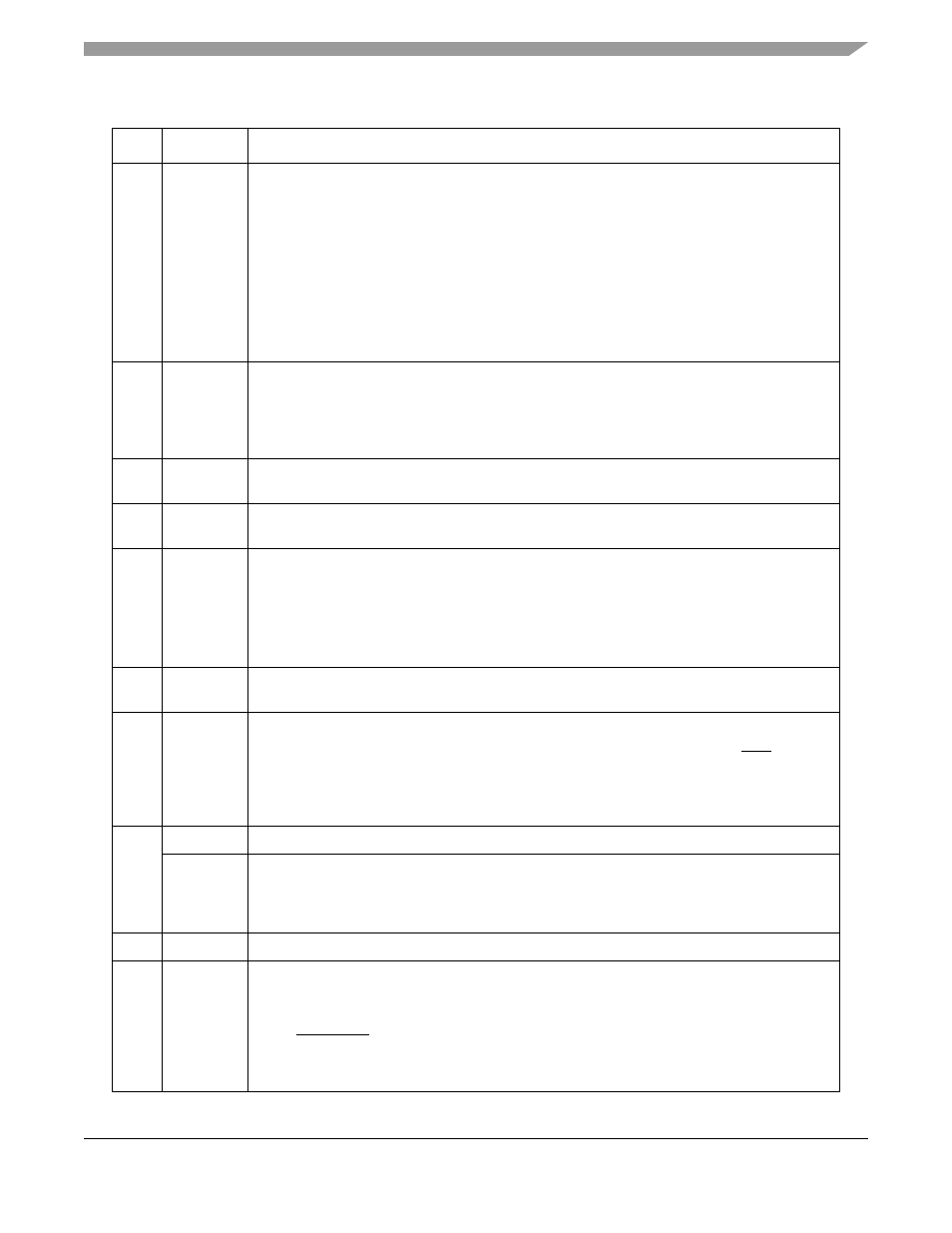

13–15

ISB

Initial internal space base select. Defines the initial value of IMMR[0–14] and determines the

base address of the internal memory space.

000 0x0000_0000

001 0x00F0_0000

010 0x0F00_0000

011 0x0FF0_0000

100 0xF000_0000

101 0xF0F0_0000

110 0xFF00_0000

111 0xFFF0_0000

See

Section 4.3.2.7, “Internal Memory Map Register (IMMR).”

16

BMS

Boot memory space. Defines the initial value for BR0[BA]. There are two possible boot memory

regions: HIMEM and LOMEM.

0 0xFE00_0000—0xFFFF_FFFF

1 0x0000_0000—0x01FF_FFFF

See

Section 11.3.1, “Base Registers (BRx).”

17

BBD

1

Bus busy disable. Defines the initial value of SIUMCR[BBD]. See

Configuration Register (SIUMCR).”

18–19

MMR

Mask masters requests. Defines the initial value of SIUMCR[MMR]. See

Module Configuration Register (SIUMCR).”

20–21

LBPC

1

Local bus pin configuration. Defines the value of SIUMCR[LBPC]. See

Module Configuration Register (SIUMCR).”

00 Local bus pins function as local bus

01 Local bus pins function as PCI bus (MPC8250, MPC8265, and MPC8266 only)

10 Local bus pins function as core pins

11 Reserved

22–23

APPC

1

Address parity pin configuration. Defines the initial value of SIUMCR[APPC]. See

Section 4.3.2.6, “SIU Module Configuration Register (SIUMCR).”

24–25

CS10PC

1

CS10 pin configuration. Defines the initial value of SIUMCR[CS10PC]. See

“SIU Module Configuration Register (SIUMCR).”

Note: During the reset configuration sequence, the BCTL1/CS10 pin toggles like POE of the 60x

bus GPCM, regardless of the configuration of the reset configuration word. After the reset

configuration sequence, the BCTL1/CS10 pin behaves according to the configuration of

SIUMCR[CS10PC].

26

—

Reserved, should be cleared.

ALD_EN

MPC8250, MPC8265, and MPC8266 only: CP auto load enable. Allows the CP to automatically

load the essential PCI configuration registers from the EEPROM during reset.

0 CP auto load is disabled.

1 CP auto load is enabled.

27

—

Reserved, should be cleared.

28–31

MODCK_H

High-order bits of the MODCK bus, which determine the clock reset configuration. See

Chapter 10, “Clocks and Power Control,”

for details. (

Note: MPC8250, MPC8265, and MPC8266 only: If the device is configured to PCI mode

(PCI_MODE is driven low), this field has no effect and the value for MODCK_H is loaded

directly from the MODCK_H pins. Note that the value of the MODCK_H bits are derived

from the dedicated PCI_MODCK_H[0:3] pins when operating in PCI mode.

Table 5-7. Hard Reset Configuration Word Field Descriptions (continued)

Bits

Name

Description