5 sssar transmit buffer descriptor, Figure 32-12. sssar txbd, Sssar transmit buffer descriptor -19 – Freescale Semiconductor MPC8260 User Manual

Page 1081: Sssar txbd -19, Sssar txbd field descriptions -19, Section 32.3.5.5, “sssar, Transmit buffer descriptor

ATM AAL2

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

32-19

32.3.5.5

SSSAR Transmit Buffer Descriptor

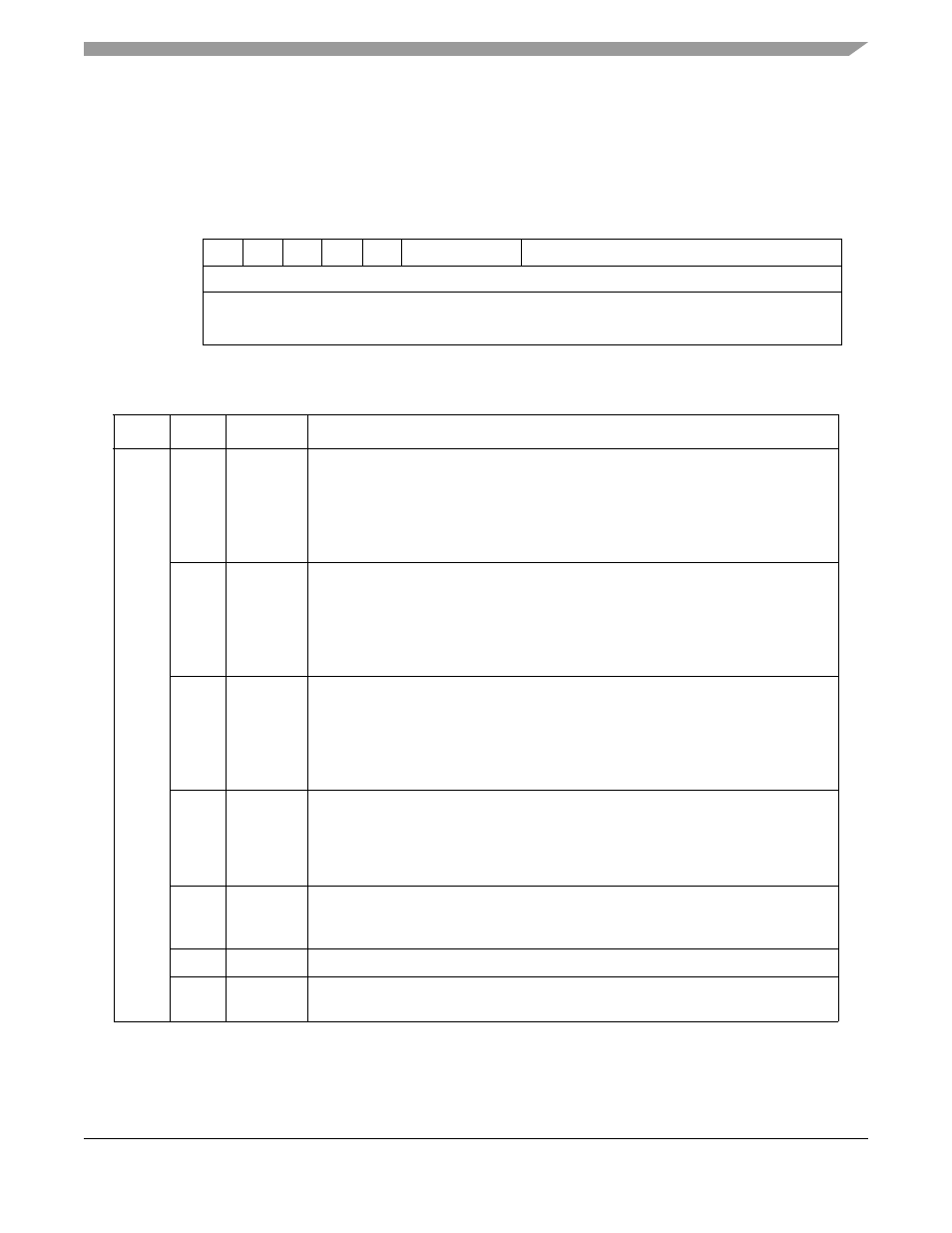

The SSSAR buffer structure consists of a BD table that points to data buffers. The buffers may contain

SSSAR SDUs belonging to different CIDs. Each buffer may contain a whole SSSAR SDU or part of it.

The CPS CID is located in the first BD of the SSSAR SDU. See

.

0

1

2

3

4

5

7

8

15

Offset + 0x00

R

CM

W

I

L

—

CID

Offset + 0x02

Data Length (DL)

Offset + 0x04

Tx Data Buffer Pointer (TXDBPTR)

Offset + 0x06

Figure 32-12. SSSAR TxBD

Table 32-5. SSSAR TxBD Field Descriptions

Offset

Bits

Name

1

Description

0x00

0

R

Ready

0 The buffer associated with this BD is not ready for transmission. The user is free to

manipulate this BD or its associated buffer. The CP clears R after the buffer is sent

or after an error condition is encountered.

1 The user-prepared buffer has not been sent or is currently being sent. No fields of

this BD may be written by the user once R is set.

1

CM

Continuous mode

0 Normal operation.

1 The CP does not clear R after this BD is closed, allowing the associated buffer to

be retransmitted automatically when the CP next accesses this BD. However, the

R bit is cleared if an error occurs during transmission, regardless of the CM bit

setting.

2

W

Wrap (final BD in table)

0 This is not the last BD in the TxBD table.

1 This is the last BD in the TxBD table. After this buffer is used, the CP transmits

outgoing data for this channel from the first BD in the table (the BD pointed to by

the channel’s TxBD_table_Base in the TxQD). The number of TxBDs in this table

is determined only by the W bit.

3

I

Interrupt

0 No interrupt is generated after this buffer has been serviced.

1 A Tx Buffer event is sent to the interrupt queue after this buffer is serviced. The

GHIN/GLIN bit in the event register is set when the INT_CNT counter reaches

terminal count.

4

L

Last.

0 This is not the last buffer of the SSSAR SDU.

1 This is the last buffer of the SSSAR SDU.

5-7

—

Reserved, should be cleared during initialization.

8-15

CID

Contains the CID number of the SSSAR SDU pointed by this BD. This field should be

written to the first BD of an SSSAR SDU.