Figure 35-7. ethernet interrupt events example, 19 ethernet rxbds, Ethernet rxbds -22 – Freescale Semiconductor MPC8260 User Manual

Page 1218: Ethernet interrupt events example -22, Figure 35-7

Fast Ethernet Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

35-22

Freescale Semiconductor

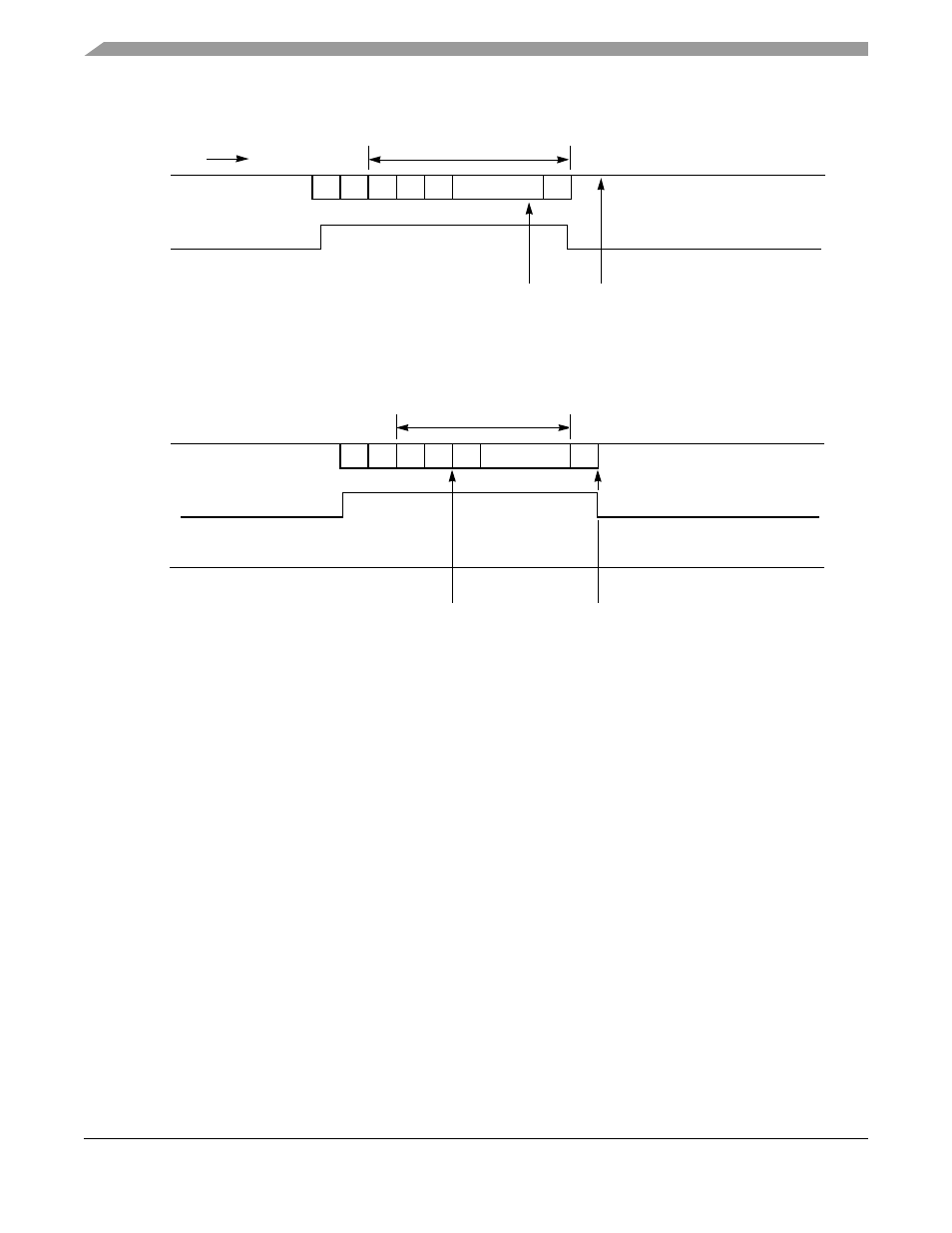

Figure 35-7. Ethernet Interrupt Events Example

NOTE

The FCC status register is not valid for the Ethernet protocol. The current

state of the MII signals can be read through the parallel ports.

35.19 Ethernet RxBDs

The Ethernet controller uses the RxBD to report information about the received data for each buffer.

shows the FCC Ethernet RxBD format.

RXB

Line Idle

Stored in Rx Buffer

RXD

RX_DV

Frame

Received in Ethernet

Time

Line Idle

TXD

TX_EN

Frame

Transmitted by Ethernet

COL

TXB, GRA

TXB

Line Idle

Line Idle

Stored in Tx Buffer

Notes:

Ethernet FCCE

Events

1. RXB event assumes receive buffers are 64 bytes each.

2. The RXF interrupt may occur later than RX_DV due to receive FIFO latency.

Notes:

Ethernet FCCE

Events

1. TXB events assume the frame required two transmit buffers.

2. The GRA event assumes a graceful stop transmit command was issued during frame transmission.

P SFD DA SA

CR

RXF

T/L

D

P SFD DA SA

CR

T/L

D

Legend:

P = Preamble, SFD = Start frame delimiter, DA and SA = Destination/Source address,

T/L = Type/Length, D = Data, CR = CRC bytes