Table 4-23. pitr field descriptions, 4 pci control registers, 1 pci base register (pcibrx) – Freescale Semiconductor MPC8260 User Manual

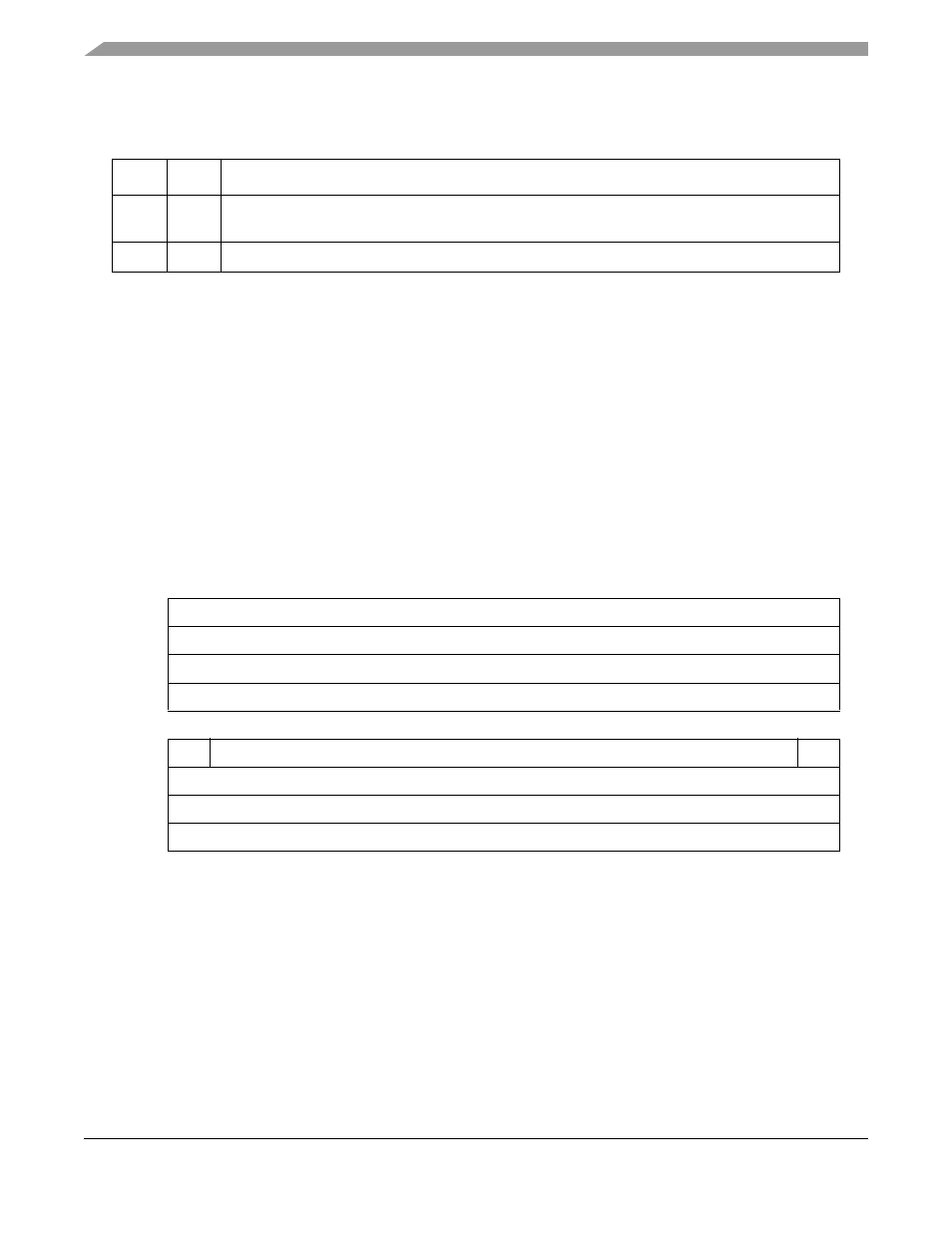

Page 220: Figure 4-41. pci base registers (pcibrx), Pci control registers -48, Pci base register (pcibrx) -48, Pci base registers (pcibrx) -48, Pitr field descriptions -48, Table 4-23 describes pitr fields, Figure 4-41 shows the pci base register

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-48

Freescale Semiconductor

describes PITR fields.

4.3.4

PCI Control Registers

NOTE

This section applies only to the MPC8250, the MPC8265, and the

MPC8266.

Two pairs of registers detect accesses from the 60x bus side to the PCI bridge (other than PCI internal

registers accesses). Each pair consists of a PCI base register (PCIBRx) for comparing addresses and a

corresponding PCI mask register (PCIMSKx).

4.3.4.1

PCI Base Register (PCIBRx)

shows the PCI base register.

Figure 4-41. PCI Base Registers (PCIBRx)

Table 4-23. PITR Field Descriptions

Bits

Name

Description

0–15

PITC

Periodic interrupt timing count. Bits 0–15 are defined as the PIT. It contains the current count

remaining for the periodic timer. Writes have no effect on this field.

16–31

—

Reserved, should be cleared.

0

15

Field

BA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x101AC (PCIBR0); 0x101B0 (PCIBR1)

16

17

30

31

Field

BA

—

V

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x101AE (PCIBR0); 0x101B2 (PCIBR1)