4 scc hdlc parameter ram, Scc hdlc parameter ram -3, Hdlc-specific scc parameter ram memory map -3 – Freescale Semiconductor MPC8260 User Manual

Page 731

SCC HDLC Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

22-3

and an address mask. The SCC compares the received address field with the user-defined values after

masking with the address mask. To detect broadcast (all ones) address frames, one address register must

be written with all ones.

If an address match is detected, the SCC fetches the next BD and SCC starts transferring the incoming

frame to the buffer if it is empty. When the buffer is full, the SCC clears RxBD[E] and generates a

maskable interrupt if RxBD[I] is set. If the incoming frame is larger than the current buffer, the SCC

continues receiving using the next BD in the table.

During reception, the SCC checks for frames that are too long (using MFLR). When the frame ends, the

CRC field is checked against the recalculated value and written to the buffer. RxBD[Data Length] of the

last BD in the HDLC frame contains the entire frame length. This also enables software to identify the

frames in which the maximum frame length violations occur. The SCC sets RxBD[L] (last buffer in

frame), writes the frame status bits, and clears RxBD[E]. It then generates a maskable event (SCCE[RXF])

to indicate a frame was received. The SCC then waits for a new frame. Back-to-back frames can be

received with only one shared flag between frames.

The received frames threshold parameter (RFTHR) can be used to postpone interrupts until a specified

number of frames is received. This function can be combined with a timer to implement a timeout if fewer

than the specified number of threshold frames is received.

Note that SCCs in HDLC mode, or any other synchronous mode, must receive a minimum of eight clocks

after the last bit arrives to account for Rx FIFO delay.

22.4

SCC HDLC Parameter RAM

For HDLC mode, the protocol-specific area of the SCC parameter RAM is mapped as in

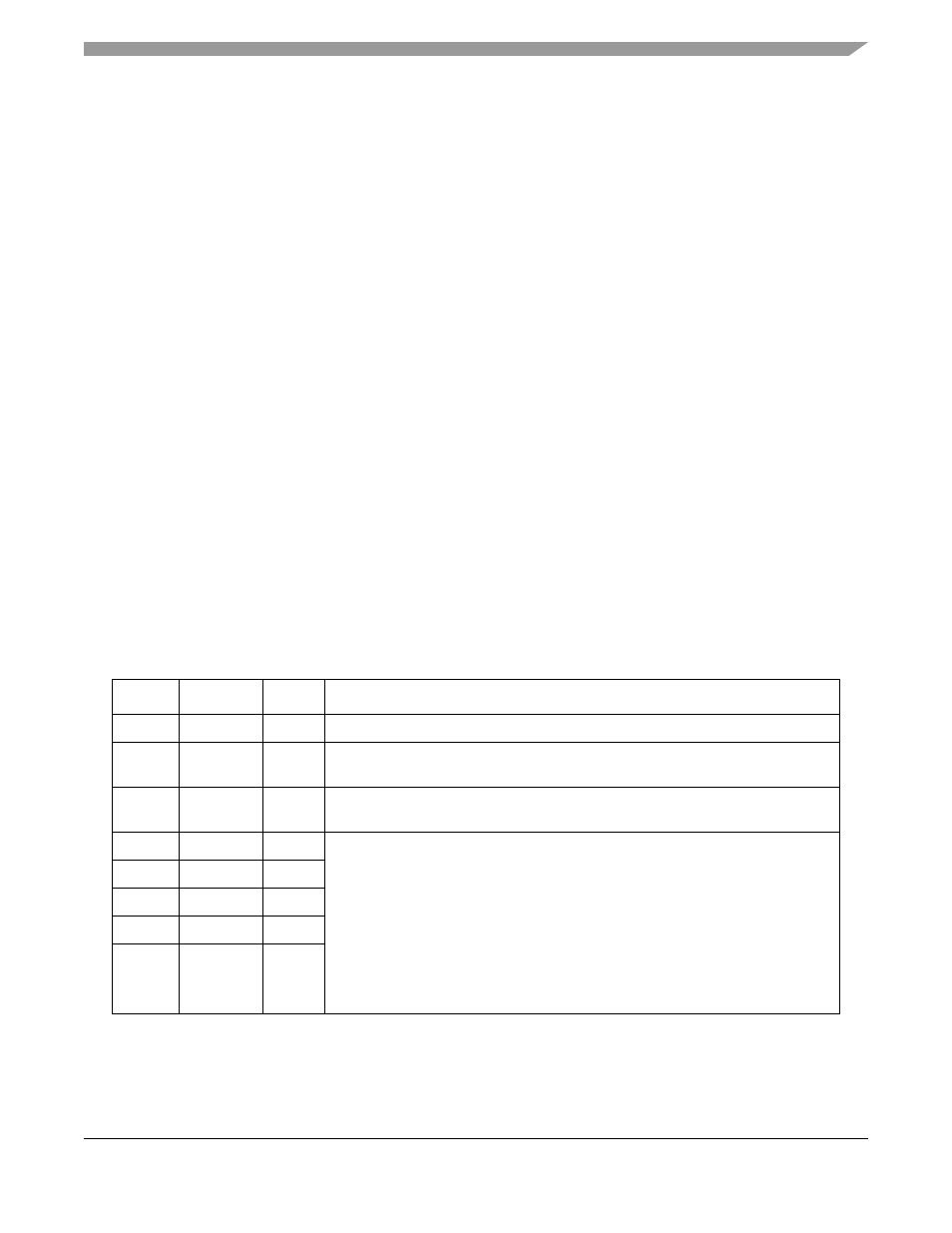

Table 22-1. HDLC-Specific SCC Parameter RAM Memory Map

Offset

1

Name

Width

Description

0x30

—

Word

Reserved

0x34

C_MASK

Word

CRC mask. For the 16-bit CRC-CCITT, initialize with 0x0000_F0B8. For 32-bit

CRC-CCITT, initialize with 0xDEBB_20E3.

0x38

C_PRES

Word

CRC preset. For the 16-bit CRC-CCITT, initialize with 0x0000_FFFF. For 32-bit

CRC-CCITT, initialize with 0xFFFF_FFFF.

0x3C

DISFC

Hword

Modulo 2

16

counters maintained by the CP. Initialize them while the channel is

disabled.

DISFC (Discarded frame counter) Counts error-free frames discarded due to lack

of free buffers.

CRCEC (CRC error counter) Includes frames not addressed to the user or frames

received in the BSY condition, but does not include overrun errors.

ABTSC (Abort sequence counter)

NMARC (Nonmatching address received counter) Includes error-free frames only.

RETRC (Frame retransmission counter) Counts number of frames resent due to

collision.

0x3E

CRCEC

Hword

0x40

ABTSC

Hword

0x42

NMARC

Hword

0x44

RETRC

Hword