4 six ram programming example, Table 15-3. six ram entry descriptions, 5 static and dynamic routing – Freescale Semiconductor MPC8260 User Manual

Page 590: Six ram programming example -14, Static and dynamic routing -14, Six ram entry descriptions -14, 4 si, Ram programming example, The si x ram has two operating modes for the tdms

Serial Interface with Time-Slot Assigner

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

15-14

Freescale Semiconductor

15.4.4

SI

x

RAM Programming Example

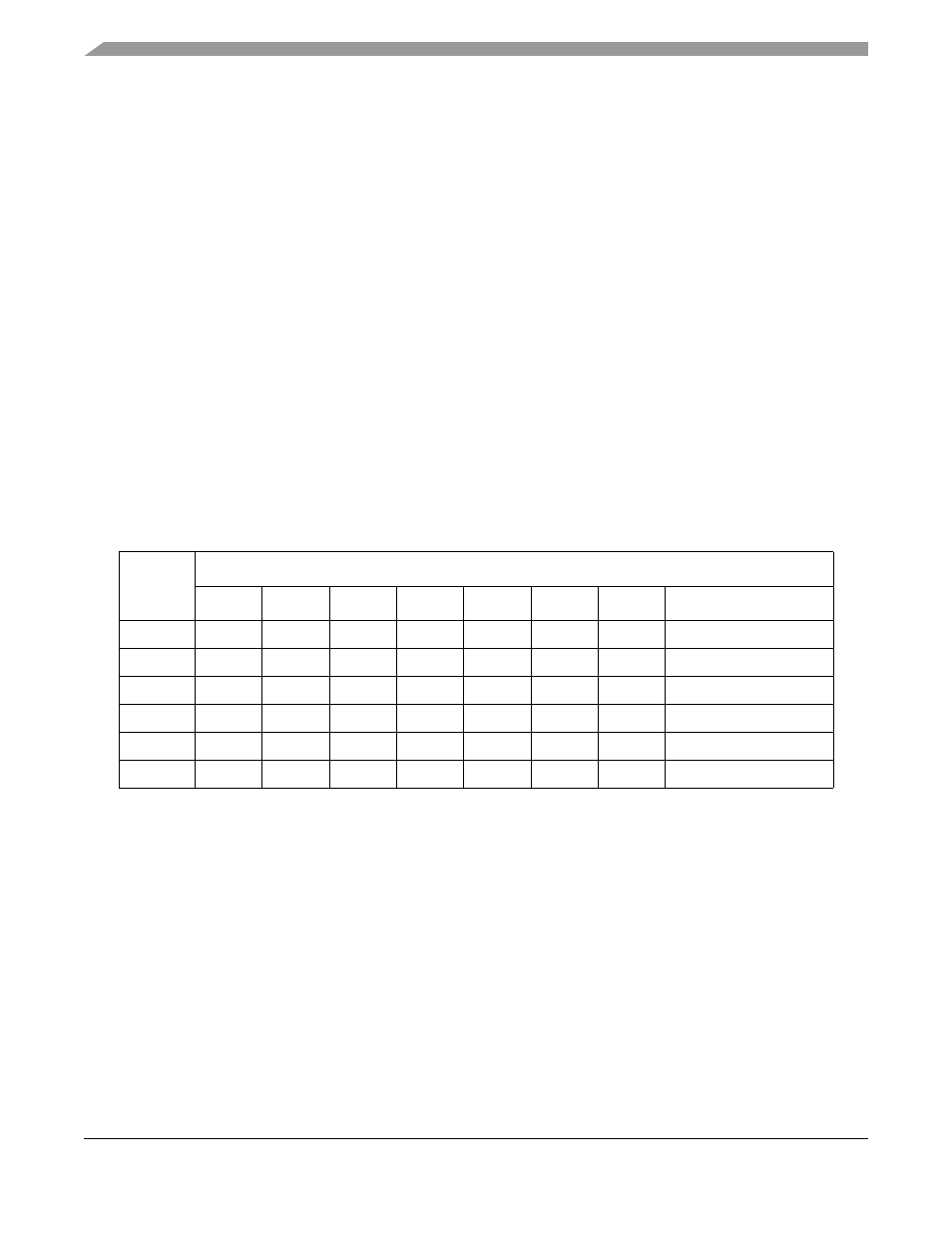

This example shows how to program the RAM to support the 10-bit IDL bus. Figure 15-23. shows the

10-bit IDL bus format. In this example, the TSA supports the B1 channel with SCC2, the D channel with

SCC1, the first 4 bits of the B2 channel with an external device (using a strobe to enable the external

device), and the last 4 bits of B2 with SMC1. Additionally, the TSA marks the D channel with another

strobe signal.

First, divide the frame from the start (the sync) to the end of the frame according to the support that is

required:

•

8 bits (B1)—SCC2

•

1 bit (D)—SCC1 + strobe 1

•

1 bit—no support

•

4 bits (B2)—strobe 2

•

4 bits (B2)—SMC1

•

1 bit (D)—SCC1 + strobe 1

Each of these six divisions can be supported by a single SIx RAM entry. Thus, six SIx RAM entries are

needed. See

NOTE

IDL requires the same routing for both receive and transmit., Therefore, an

exact duplicate of the above entries should be written to both the receive and

transmit sections of the SIx RAM. Then SIxMR[CRTx] can be used to

instruct the SIx RAM to use the same clock and sync to simultaneously

control both sets of SIx RAM entries.

15.4.5

Static and Dynamic Routing

The SIx RAM has two operating modes for the TDMs:

Table 15-3. SI

x RAM Entry Descriptions

Entry

Number

SI

x

RAM Entry

MCC

SWTR

SSEL

CSEL

CNT

BYT

LST

Description

0

0

0

0000

0010

000

1

0

8-bit SCC2

1

0

0

1000

0001

000

0

0

1-bit SCC1 strobe1

2

0

0

0000

0000

000

0

0

1-bit no support

3

0

0

0100

0000

011

0

0

4-bit strobe2

4

0

0

0000

0101

011

0

0

4-bit SMC1

5

0

0

1000

0001

000

0

1

1-bit SCC1 strobe1