Table 9-70. dmadarx field descriptions, 6 dma byte count register [0-3] (dmabcrx), Dma byte count register [0–3] (dmabcrx) -93 – Freescale Semiconductor MPC8260 User Manual

Page 399: Dmadarx field descriptions -93, Section 9.13.1.6.6, “dma byte count, Register [0–3] (dmabcrx), Figure 9-86, Table 9-71 describes dmabcr x fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-93

The choice between PCI or 60x is done according to the following rule: If the address hits one of the PCI

outbound windows, then the destination data is written to the PCI memory. Otherwise, it is written to the

60x memory. Refer to

.

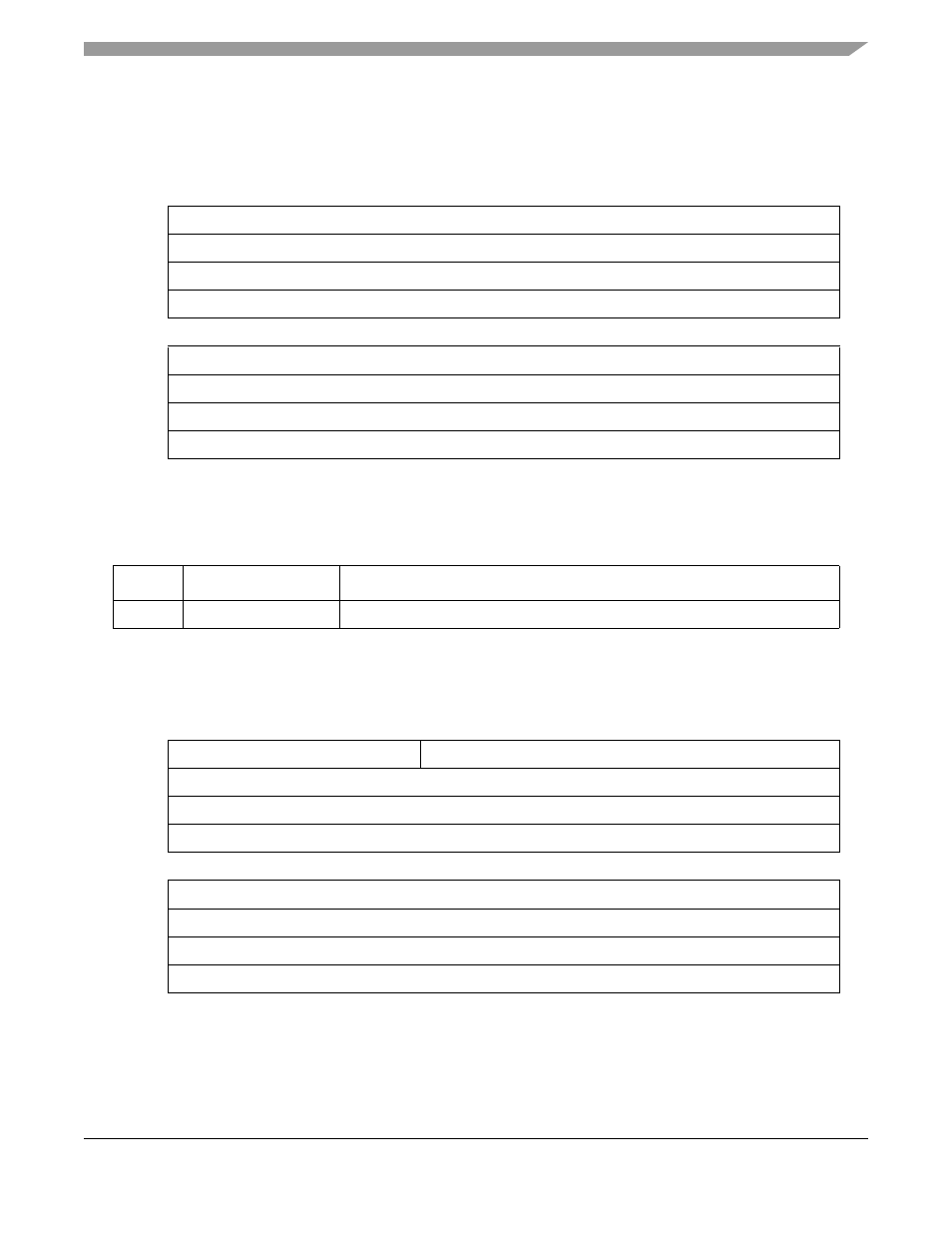

Figure 9-86. DMA Destination Address Register [0–3] (DMADAR

x)

describes DMADARx fields.

9.13.1.6.6

DMA Byte Count Register [0–3] (DMABCR

x

)

This register contains the number of bytes per transfer (maximum transfer size is 64 Mbytes).

Figure 9-87. DMA Byte Count Register [0–3] (DMABCR

x)

describes DMABCRx fields.

31

16

Field

DA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x1051A (DMAADAR0); 0x1059A (DMAADAR1); 0x1061A (DMAADAR2); 0x1069A (DMAADAR3)

15

0

Field

DA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10518 (DMAADAR0); 0x10598 (DMAADAR1); 0x10618 (DMAADAR2); 0x10698 (DMAADAR3)

Table 9-70. DMADAR

x Field Descriptions

Bit

Name

Description

31–0

DA

Destination address. The content is updated after every DMA write operation.

31

26

25

16

Field

—

BC

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10522 (DMABCR0); 0x105A2(DMABCR1); 0x10622 (DMABCR2); 0x106A2 (DMABCR3)

15

0

Field

BC

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10520 (DMABCR0); 0x105A0 (DMABCR1); 0x10620 (DMABCR2); 0x106A0 (DMABCR3)