Figure 9-37. revision id register, Table 9-24. revision id register description, 6 pci bus programming interface register – Freescale Semiconductor MPC8260 User Manual

Page 356: 7 subclass code register, Pci bus programming interface register -50, Subclass code register -50, Revision id register -50, Revision id register description -50, Figure 9-37, Table 9-24

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-50

Freescale Semiconductor

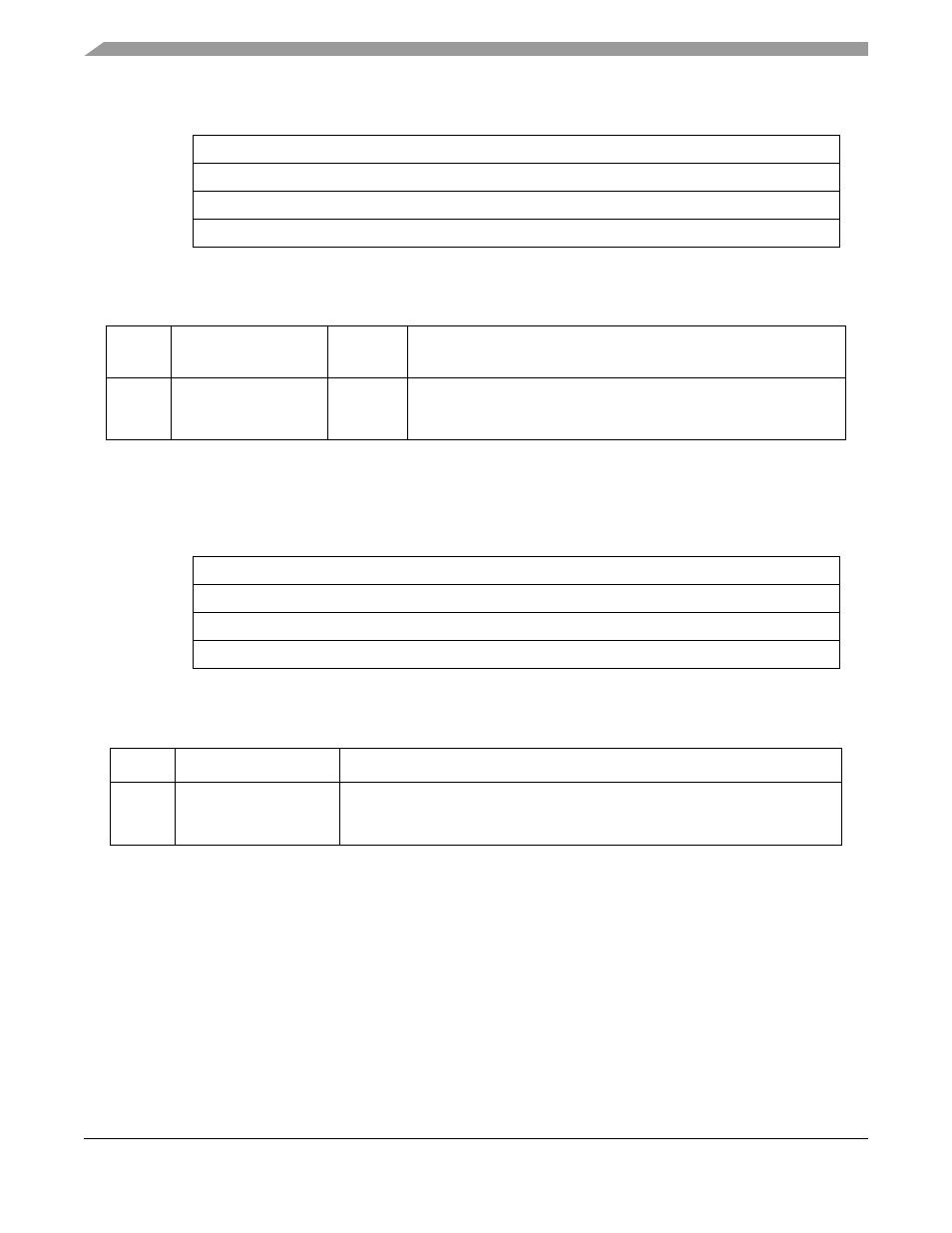

Figure 9-37. Revision ID Register

9.11.2.6

PCI Bus Programming Interface Register

describe the PCI bus programming interface register.

Figure 9-38. PCI Bus Programming Interface Register

9.11.2.7

Subclass Code Register

describe the subclass code register.

7

0

Field

RID

Reset

Refer to

R/W

R

Addr

0x08

Table 9-24. Revision ID Register Description

Bits

Name

Reset

Value

Description

7–0

Revision ID

Revision

Dependent

Specifies a device-specific revision code for the PowerQUICC II

(assigned by Freescale). Revision ID = 0x11 for .25 micron revisions

A.0, B.1, and C.0

7

0

Field

PI

Reset

Refer to

R/W

R

Addr

0x09

Table 9-25. PCI Bus Programming Interface Register Description

Bits

Name

Description

7–0

Programming interface

0x00 When the PCI bridge is configured as host bridge.

0x01 When the PCI bridge is configured as a peripheral device to indicate the

programming model supports the I

2

O interface.