Table 35-9. fcce/fccm field descriptions, Fcce/fccm field descriptions -21 – Freescale Semiconductor MPC8260 User Manual

Page 1217

Fast Ethernet Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

35-21

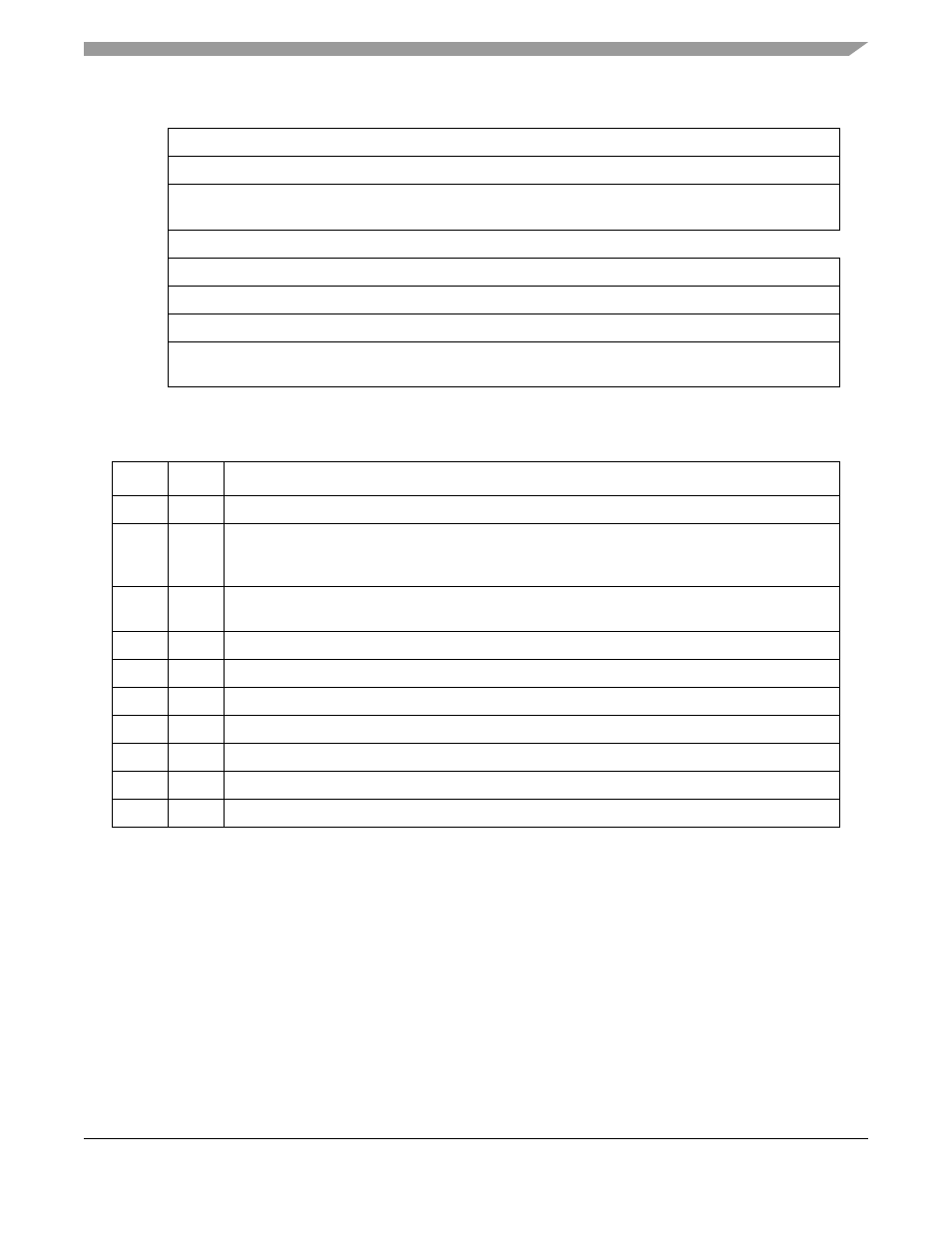

describes FCCE/FCCM fields.

shows interrupts that can be generated in the Ethernet protocol.

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x0x11310 (FCCE1), 0x0x11330 (FCCE2), 0x0x11350 (FCCE3)/

0x0x11314 (FCCM1), 0x0x11334 (FCCM2), 0x0x11354 (FCCM3)

16

31

Field

—

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x11312 (FCCE1), 0x11332 (FCCE2), 0x11352 (FCCE3)/

0x11316 (FCCM1), 0x11336 (FCCM2), 0x11356 (FCCM3)

Table 35-9. FCCE/FCCM Field Descriptions

Bits

Name

Description

0–7

—

Reserved, should be cleared.

8

GRA

Graceful stop complete. A graceful stop, initiated by the

GRACEFUL

STOP

TRANSMIT

command, is

complete. When the command is issued, GRA is set as soon the transmitter finishes sending a

frame in progress. If no frame is in progress, GRA is set immediately.

9

RXC

RX control. A control frame has been received (FSMR[FCE] must be set). As soon as the transmitter

finishes sending the current frame, a pause operation is performed.

10

TXC

TX control. An out-of-sequence frame was sent.

11

TXE

Tx error. An error occurred on the transmitter channel.

12

RXF

Rx frame. Set when a complete frame is received on the Ethernet channel.

13

BSY

Busy condition. Set when a frame is received and discarded due to a lack of buffers.

14

TXB

Tx buffer. Set when a buffer has been sent on the Ethernet channel.

15

RXB

Rx buffer. A buffer that was not a complete frame is received on the Ethernet channel.

16–31

—

Reserved, should be cleared.

Figure 35-6.

Ethernet Event Register (FCCE)/Mask Register (FCCM)