12 sending a break (transmitter), 13 sending a preamble (transmitter), 14 fractional stop bits (transmitter) – Freescale Semiconductor MPC8260 User Manual

Page 714: Figure 21-5. asynchronous uart transmitter, Sending a break (transmitter) -10, Sending a preamble (transmitter) -10, Fractional stop bits (transmitter) -10, Asynchronous uart transmitter -10, Table 21-6 describes dsr fields

SCC UART Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

21-10

Freescale Semiconductor

21.12 Sending a Break (Transmitter)

A break is an all-zeros character with no stop bit that is sent by issuing a

STOP

TRANSMIT

command. The

SCC finishes transmitting outstanding data, sends a programmable number of break characters

(determined by BRKCR), and reverts to idle or sends data if a

RESTART

TRANSMIT

command is given

before completion. When the break code is complete, the transmitter sends at least one high bit before

sending more data, to guarantee recognition of a valid start bit. Because break characters do not preempt

characters in the transmit FIFO, they may not be sent for eight (SCC) or four (SCC) character times. To

reduce this latency, set GSMR_H[TFL] to decrease the FIFO size to one character before enabling the

transmitter.

21.13 Sending a Preamble (Transmitter)

Sending a preamble sequence of consecutive ones ensures that a line is idle before sending a message. If

the preamble bit TxBD[P] is set, the SCC sends a preamble sequence (idle character) before sending the

buffer. For example, for 8 data bits, no parity, 1 stop bit, and 1 start bit, a preamble of 10 ones is sent before

the first character in the buffer.

21.14 Fractional Stop Bits (Transmitter)

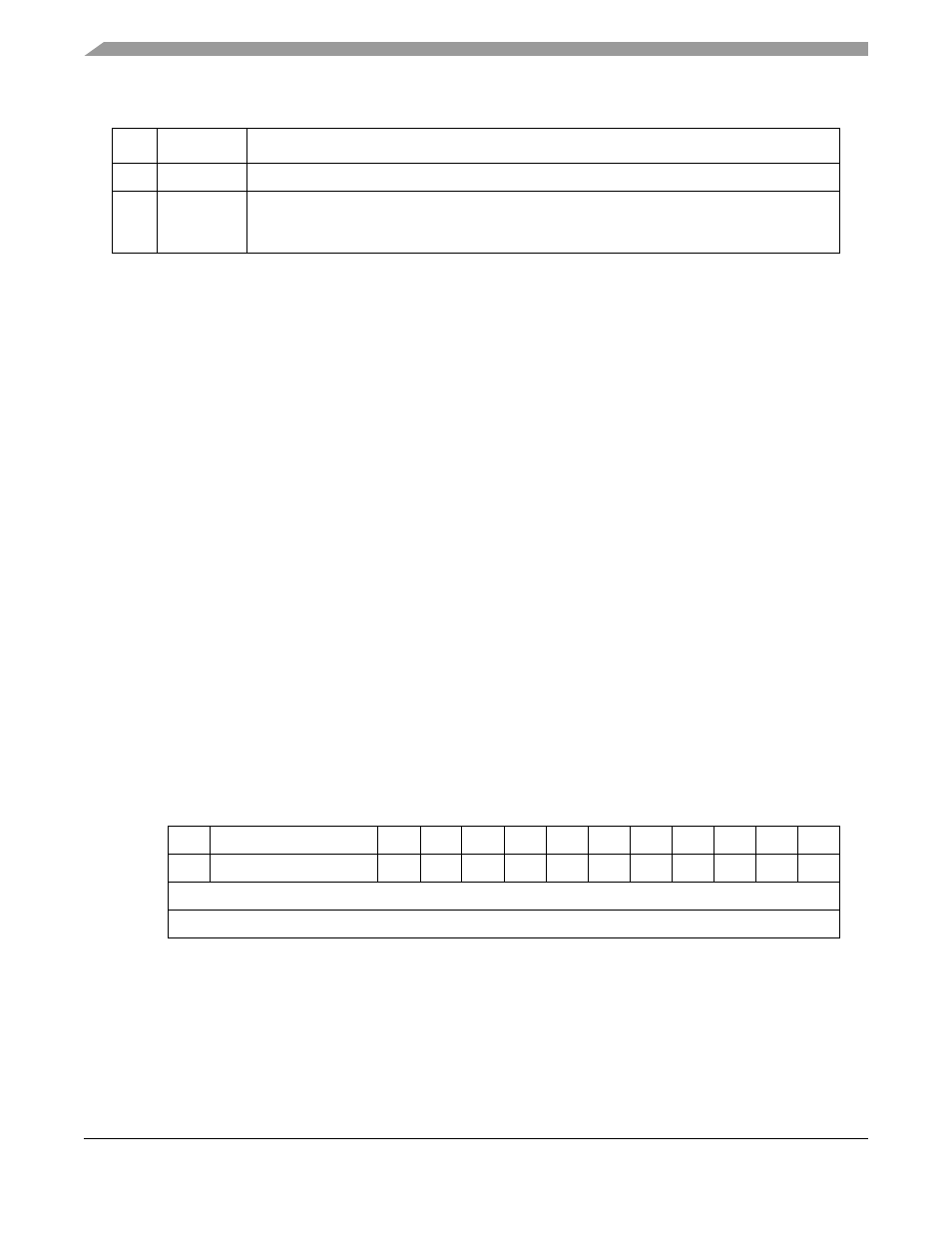

The asynchronous UART transmitter, shown in

, can be programmed to send fractional stop

bits. The FSB field in the data synchronization register (DSR) determines the fractional length of the last

stop bit to be sent. FSB can be modified at any time. If two stop bits are sent, only the second is affected.

Idle characters are always sent as full-length characters

.

describes DSR fields.

7

A

Address. Setting this bit indicates an address character for multidrop mode.

8–15 CHARSEND Character send. Contains the character to be sent. Any 5- to 8-bit character value can be sent

in accordance with the UART configuration. The character should be placed in the lsbs of

CHARSEND. This value can be changed only while REA = 0.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

—

FSB

—

—

—

—

—

—

—

—

—

—

—

Reset

0

1111

1

1

0

0

1

1

1

1

1

1

0

R/W

R/W

Addr

Figure 21-5. Asynchronous UART Transmitter

Table 21-5. TOSEQ Field Descriptions (continued)

Bit

Name

Description