11 configuration registers, 1 memory-mapped configuration registers, Table 9-3. internal memory map (continued) – Freescale Semiconductor MPC8260 User Manual

Page 333: Configuration registers -27, Memory-mapped configuration registers -27, Internal memory map -27, Bed in

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-27

9.11

Configuration Registers

There are two types of configuration registers in the PCI bridge: PCI-specified and memory-mapped. The

PCI-specified type,

referred to as PCI configuration registers, are accessed through PCI configuration

cycles (refer to

Section 9.11.2, “PCI Bridge Configuration Registers”

). The memory-mapped

configuration registers are placed in the internal memory map of the PowerQUICC II and are accessed like

other internal registers (refer to

Section 9.11.1, “Memory-Mapped Configuration Registers”

).

Both the PCI configuration and memory-mapped internal registers of the PCI bridge are intrinsically

little-endian and are described using classic bit-numbering; that is, the lowest memory address contains

the least significant byte of the register and bit 0 is the least-significant bit of the register.

NOTE: Accessing Configuration Registers

For a PCI device to share little-endian (LE) data with the 603e core CPU,

software must byte-swap the data of the configuration register. Refer to

Section 9.11.2.27, “PCI Configuration Register Access in Big-Endian

Mode,”

Section 9.11.2.27.1, “Additional Information on Endianess.”

Also note that reserved bits in the configuration registers are not guaranteed to have predictable values.

Software must preserve the values of reserved bits when writing to a configuration register. Also, when

reading from a configuration register, software should not rely on the value of reserved bits remaining

constant.

NOTE: Accessing PCI Registers in Non-PCI Mode

In non-PCI mode, a 60x bus master should not attempt to access the PCI

memory mapped configuration registers. Doing so will cause the internal

memory space of the PowerQUICC II to be inaccessible. Any following

access to the internal memory space will not be terminated normally, and

can only be terminated by TEA if the 60x bus monitor is activated. The

system can recover only after a soft reset.

9.11.1

Memory-Mapped Configuration Registers

describes the memory-mapped configuration registers provided by the PCI bridge. Note that

memory gaps not defined are reserved and should not be accessed.

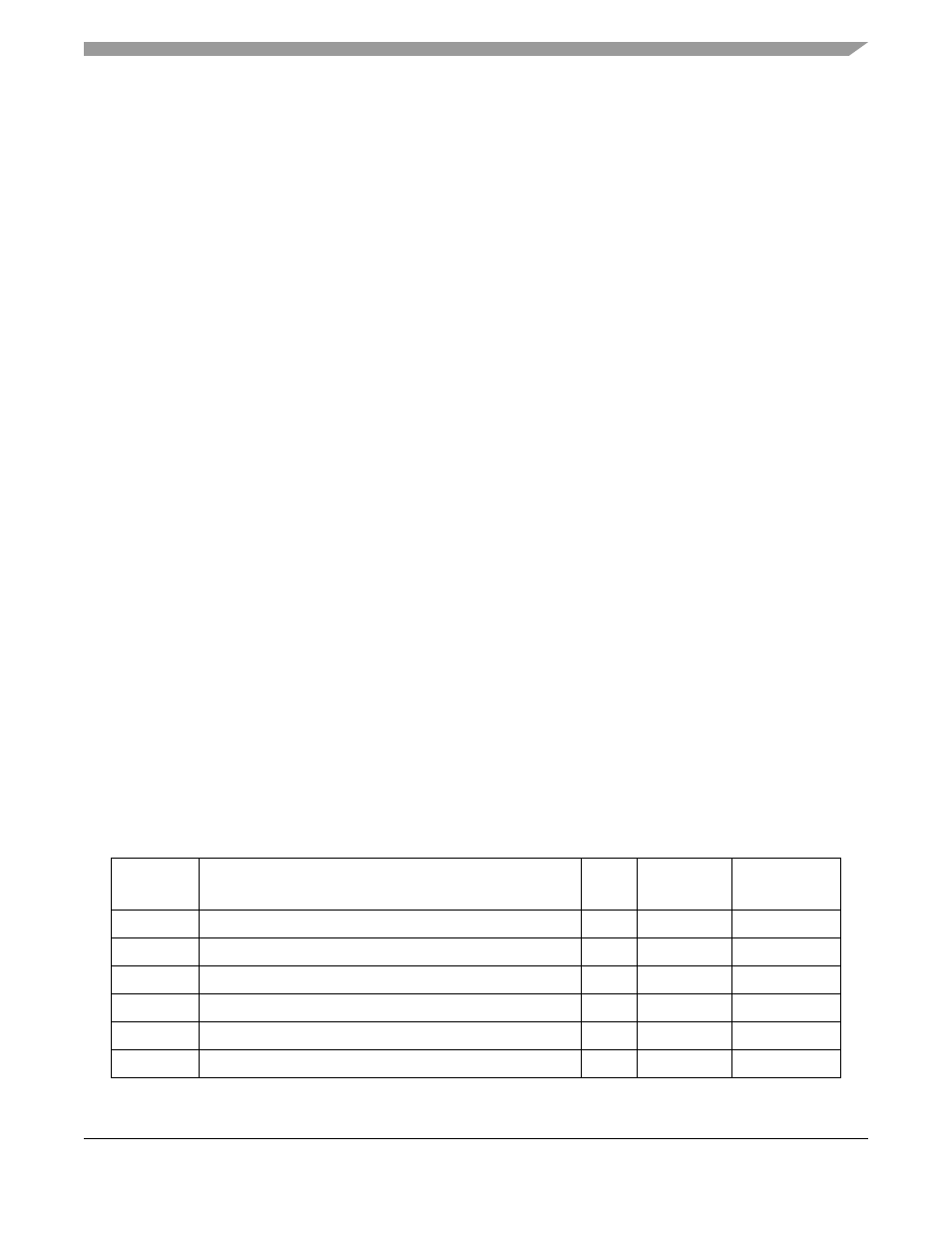

Table 9-3. Internal Memory Map

Address

(offset)

Register

Access

Reset

Section/Page

0x10430

Outbound interrupt status register (OMISR)

special 0x0000_0000

0x10434

Outbound interrupt mask register (OMIMR)

R/W

0x0000_0000

0x10440

Inbound FIFO queue port register (IFQPR)

R/W

0x0000_0000

0x10444

Outbound FIFO queue port register (OFQPR)

R/W

0x0000_0000

0x10450

Inbound message register 0 (IMR0)

R/W

undefined

0x10454

Inbound message register 1 (IMR1)

R/W

undefined