Freescale Semiconductor MPC8260 User Manual

Page 285

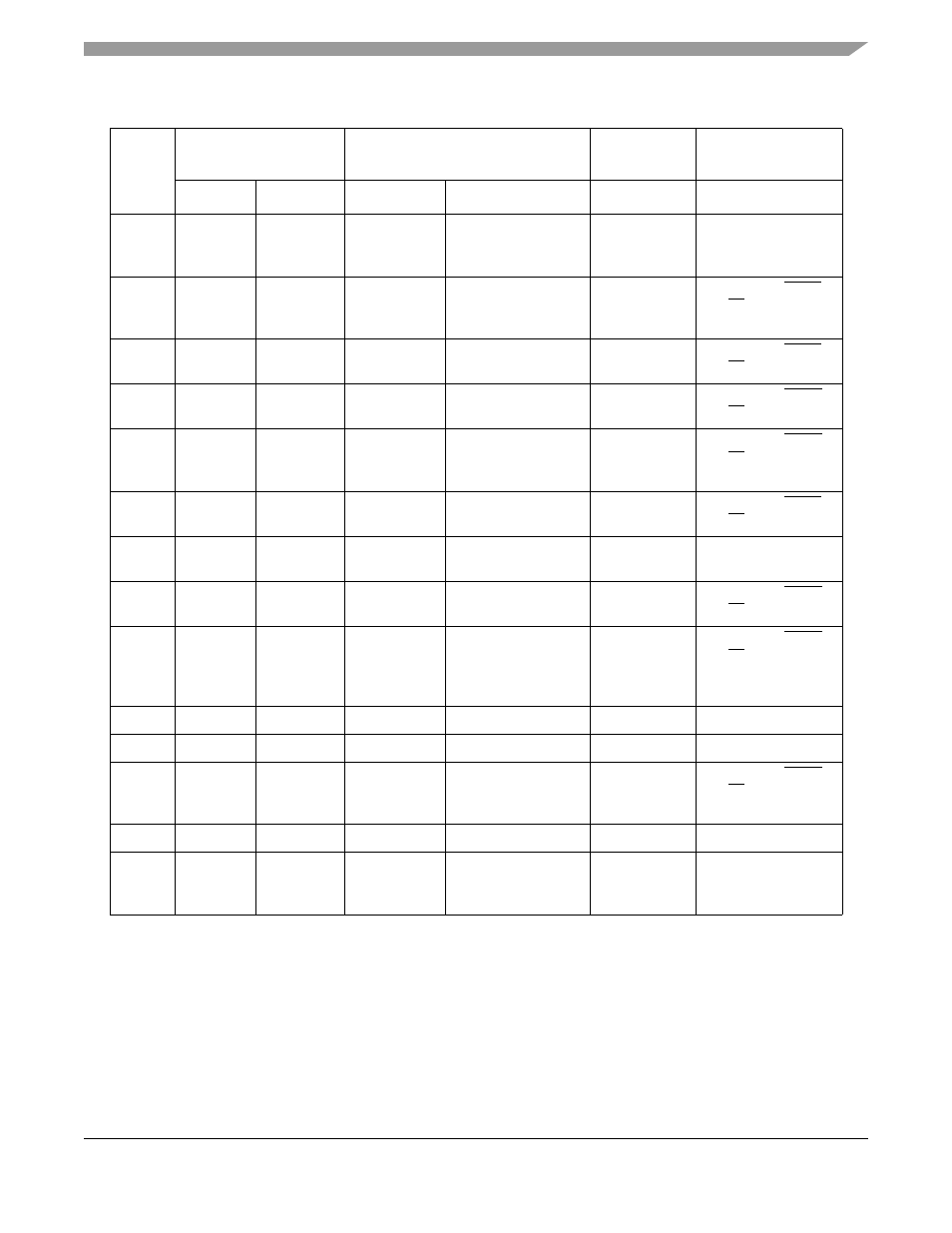

The 60x Bus

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

8-11

NOTE

Regarding

1XX01

Reserved

for

customer

—

Not applicable Not applicable

Not applicable

Illegal

00010

WR w/flush Single-beat

write or

Burst

Single-beat

write

CI, WT store, or

non-processor master

under

Flush, cancel

reservation

Write, assert AACK

and TA.

00110

WR w/Kill

Burst

Burst

(non-GLB)

Castout, ca-op push,

or snoop copyback

Kill, cancel

reservation

Write, assert AACK

and TA.

01010

Read

Single-beat

read or burst

Single-beat

read

CI load, CI I-fetch or

nonprocessor master

Clean or flush

Read, assert AACK

and TA.

01110

Read with

intent to

modify

Burst

Burst

Load miss, store

miss, or I-fetch

Flush

Read, assert AACK

and TA.

10010

WR w/flush

atomic

Single-beat

write

Single-beat

write

stwcx

Flush, cancel

reservation

Write, assert AACK

and TA

10110

Reserved

Not

applicable

Not applicable Not applicable

Not applicable

Illegal

11010

Read

atomic

Single-beat

read or burst

Single-beat

read

lwarx (CI load)

Clean or flush

Read, assert AACK

and TA

11110

Read with

intent to

modify

atomic

Burst

Burst

lwarx (load miss)

Flush

Read, assert AACK

and TA

00011

Reserved

—

Not applicable Not applicable

Not applicable

Illegal

00111

Reserved

—

Not applicable Not applicable

Not applicable

Illegal

01011

Read with

no intent to

cache

Single-beat

read or burst

Not applicable Not applicable

Clean

Read, assert AACK

and TA

01111

Reserved

—

Not applicable Not applicable

Not applicable

Illegal

1XX11

Reserved

for

customer

—

Not applicable Not applicable

Not applicable

Illegal

1

TT1 can be interpreted as a read-versus-write indicator for the bus.

2

This column specifies the TT encoding for the general 60x protocol. The processor generates or snoops only a subset

of those encodings.

Table 8-2. Transfer Type Encoding (continued)

TT[0–4]

1

60x Bus Specification

2

PowerQUICC II as Bus Master

PowerQUICC I

I as Snooper

PowerQUICC II

as Slave

Command Transaction

Bus Trans.

Transaction Source

Action on Hit

Action on Slave Hit