Table 27-12. smc transparent error conditions, 8 smc transparent rxbd, Figure 27-13. smc transparent rxbd – Freescale Semiconductor MPC8260 User Manual

Page 838: Smc transparent rxbd -26, Smc transparent error conditions -26, Smc transparent rxbd field descriptions -26

Serial Management Controllers (SMCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

27-26

Freescale Semiconductor

27.4.8

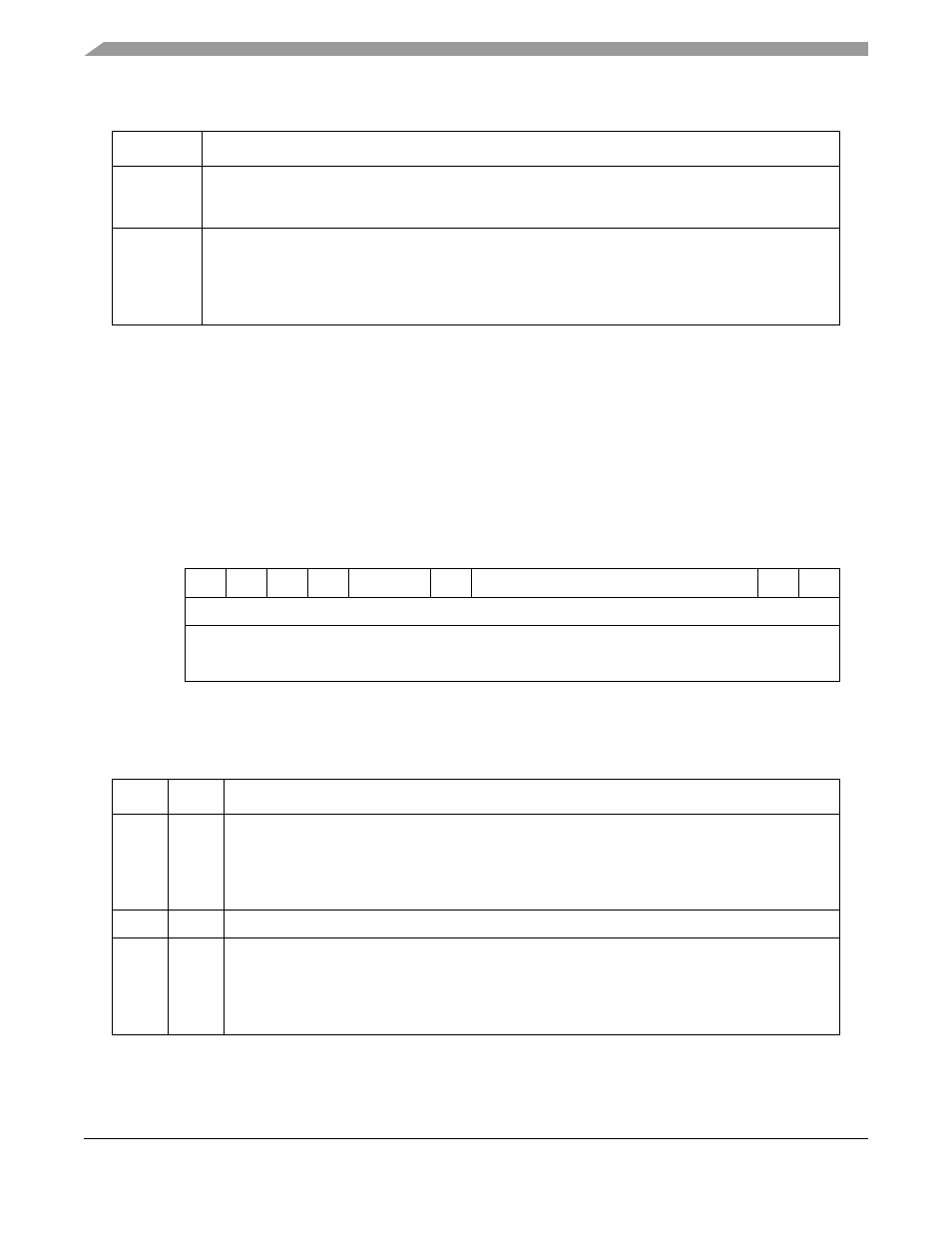

SMC Transparent RxBD

Using BDs, the CP reports information about the received data for each buffer and closes the current

buffer, generates a maskable interrupt, and starts to receive data into the next buffer after one of the

following events:

•

An overrun error occurs.

•

A full receive buffer is detected.

•

The

ENTER

HUNT

MODE

command is issued.

describes SMC transparent RxBD fields.

Table 27-12. SMC Transparent Error Conditions

Error

Descriptions

Underrun

The channel stops sending the buffer, closes it, sets UN in the BD, and generates a TXE interrupt if it is

enabled. The channel resumes sending after a

RESTART

TRANSMIT

command. Underrun cannot occur

between frames.

Overrun

The SMC maintains an internal FIFO for receiving data. If the buffer is in external memory, the CP

begins programming the SDMA channel when the first character is received into the FIFO. If a FIFO

overrun occurs, the SMC writes the received data character over the previously received character. The

previous character and its status bits are lost. Then the channel closes the buffer, sets OV in the BD,

and generates the RXB interrupt if it is enabled. Reception continues as normal.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Offset + 0

E

—

W

I

—

CM

—

OV

—

Offset + 2

Data Length

Offset + 4

Rx Data Buffer Pointer

Offset + 6

Figure 27-13. SMC Transparent RxBD

Table 27-13. SMC Transparent RxBD Field Descriptions

Bits

Name

Description

0

E

Empty.

0 The buffer is full or reception was aborted due to an error. The core can read or write any fields

of this RxBD. The CP does not use this BD while E = 0.

1 The buffer is empty or is receiving data. The CP owns this RxBD and its buffer. Once E is set, the

core should not write any fields of this RxBD.

1

—

Reserved, should be cleared.

2

W

Wrap (last BD in RxBD table).

0 Not the last BD in the table.

1 Last BD in the table. After this buffer is used, the CP receives incoming data into the first BD that

RBASE points to. The number of RxBDs is determined only by the W bit and overall space

constraints of the dual-port RAM.