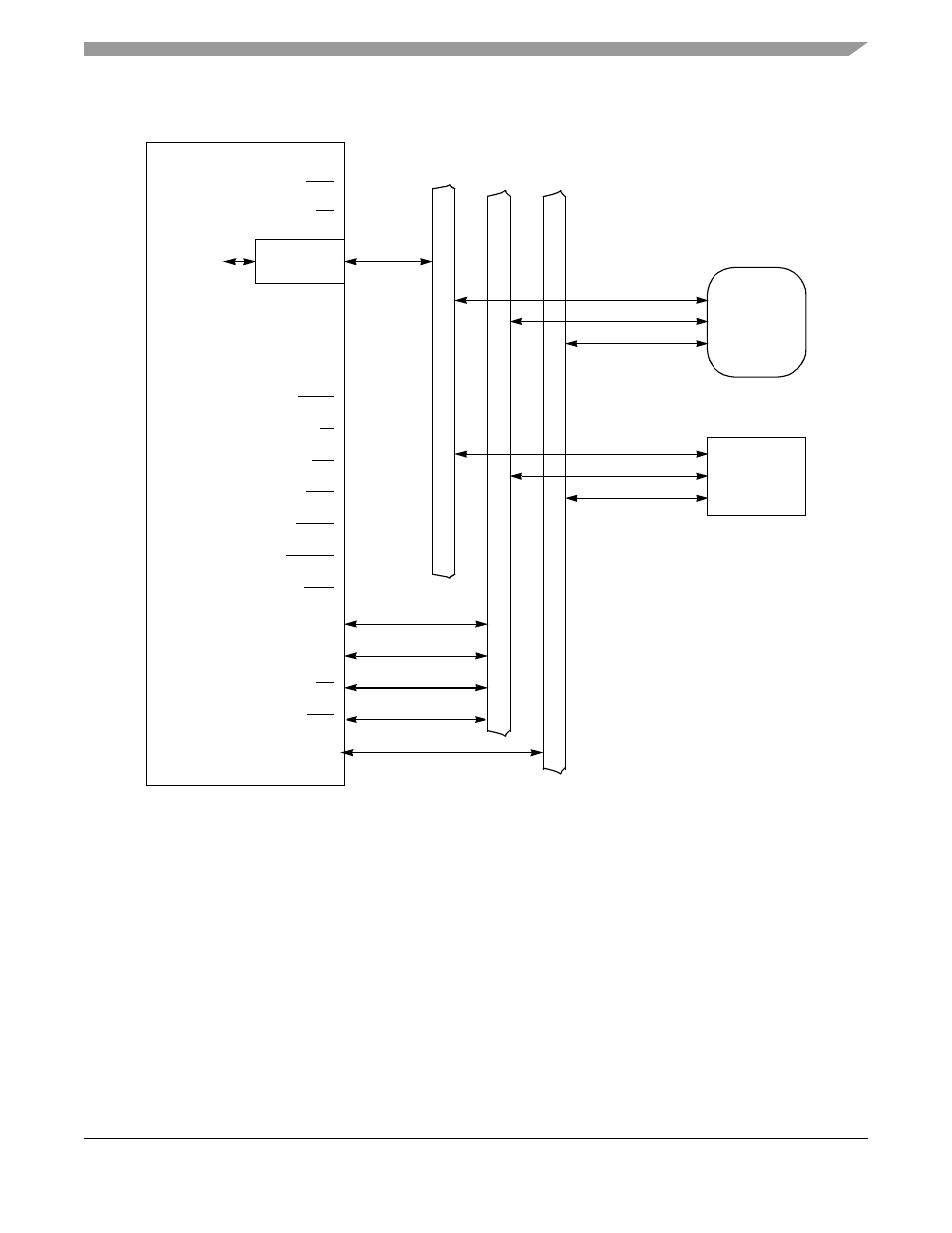

Figure 8-1. single-powerquicc ii bus mode, 2 60x-compatible bus mode, 60x-compatible bus mode -3 – Freescale Semiconductor MPC8260 User Manual

Page 277: Single-powerquicc ii bus mode -3, Section 8.2.2, “60x-compatible bus mode, Figure 8-1

The 60x Bus

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

8-3

Figure 8-1. Single-PowerQUICC II Bus Mode

NOTE

In single-PowerQUICC II bus mode, the PowerQUICC II uses the address

bus as a memory address bus. Slaves cannot use the 60x bus signals because

the addresses have memory timing, not address tenure timing.

8.2.2

60x-Compatible Bus Mode

The 60x-compatible bus mode can include one or more potential external masters (for example, an L2

cache, an ASIC DMA, a high-end processor that implements the PowerPC architecture, or a second

PowerQUICC II). When operating in a multiprocessor configuration, the PowerQUICC II snoops bus

TS

A[0–31]

TT[0–4]

TSIZ[0–3]

TBST

CI

WT

GBL

AACK

ARTRY

DBG

D[0–63]

DP[0–7]

TA

TEA

PowerQUICC II

I/O

MEM

D

a

ta

+

A

ttr

ib

u

te

s

A

ddr

e

ss +

At

tr

ibut

es

Latch &

M

e

m

o

ry

Cont

ro

lle

r Si

gnal

s

DRAM MUX

Memory Control Signals

APE