Figure 14-9. risc timer table ram usage, Table 14-11. risc timer table parameter ram, Risc timer table ram usage -23 – Freescale Semiconductor MPC8260 User Manual

Page 571: Risc timer table parameter ram -23, Figure 14-9

Communications Processor Module Overview

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

14-23

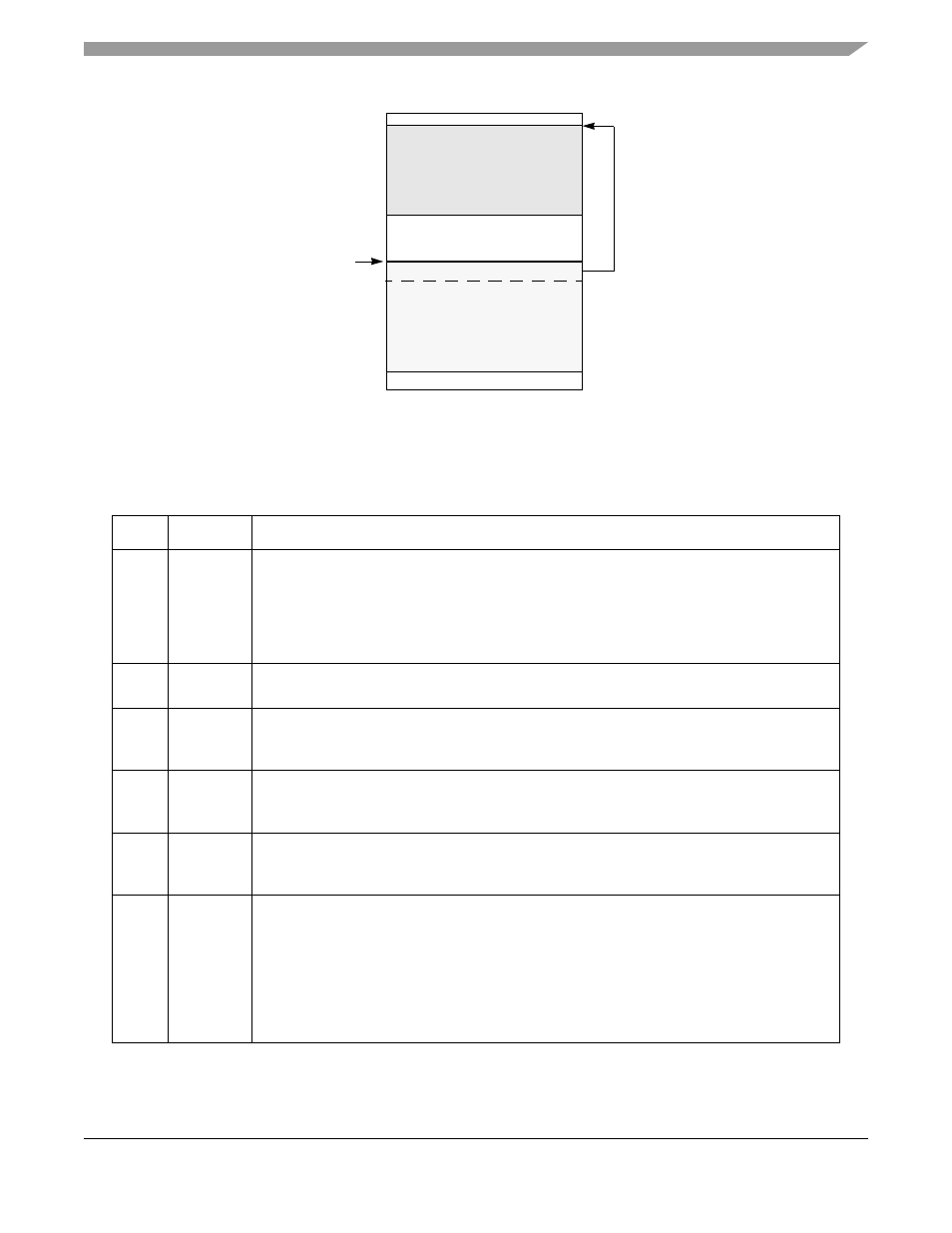

Figure 14-9. RISC Timer Table RAM Usage

The RISC timer table parameter RAM area begins at the RISC timer base address and is used for the

general timer parameters; see

.

Table 14-11. RISC Timer Table Parameter RAM

Offset

1

1

Offset from timer base address (0x8AE0)

Name

Description

0x00

TM_BASE

RISC timer table base address. The actual timers are a small block of memory in the dual-port

RAM. TM_BASE is the offset from the beginning of the dual-port RAM where that block resides.

Four bytes must be reserved at the TM_BASE for each timer used, (64 bytes if all 16 timers are

used). If fewer than 16 timers are used, timers should be allocated in ascending order to save

space. For example, only 8 bytes are required if two timers are needed and RISC timers 0 and

1 are enabled. TM_BASE should be word-aligned.

0x02

TM_PTR

RISC timer table pointer. This value is used exclusively by the CP to point to the next timer

accessed in the timer table. It should not be modified by the user.

0x04

R_TMR

RISC timer mode register. This value is used exclusively by the CP to store the mode of the

timer—one-shot (bit is 0) or restart (bit is 1). R_TMR should not be modified by the user. The

SET

TIMER

command should be used instead.

0x06

R_TMV

RISC timer valid register. Used exclusively by the CP to determine if a timer is currently

enabled. If the corresponding timer is enabled, a bit is 1. R_TMV should not be modified by the

user. The

SET

TIMER

command should be used instead.

0x08

TM_CMD

RISC timer command register. Used as a parameter location when the

SET

TIMER

command is

issued. The user should write this location before issuing the

SET

TIMER

command. This register

is defined in

Section 14.6.2, “RISC Timer Command Register (TM_CMD)

0x0C

TM_CNT

RISC timer internal count. A tick counter that the CP updates after each tick. The update occurs

after the CP complete scanning the timer table.All 16 timers are scanned every tick interval

regardless of whether any of them is enabled.It is updated if the CP’s internal timer is enabled,

regardless of whether any of the 16 timers are enabled and it can be used to track the number

of ticks the CP receives and responds to.TM_CNT is updated only after the last timer (timer 15)

has been serviced. If the CP is so busy with other tasks that it does not have time to service all

the timers during a tick interval, and timer 15 has not been serviced, then TM_CNT would not

be updated in that tick interval.

TM_BASE

16 RISC

Timer Table

Entries

(Up to 64 Bytes)

RISC

Timer Table

Parameter RAM

0x8AE0

Timer Table Base Pointer