Figure 27-17. smc c/i channel rxbd, 8 smc gci c/i channel txbd, Figure 27-18. smc c/i channel txbd – Freescale Semiconductor MPC8260 User Manual

Page 846: Smc gci c/i channel txbd -34, Smc c/i channel rxbd -34, Smc c/i channel txbd -34, Smc c/i channel rxbd field descriptions -34, Smc c/i channel txbd field descriptions -34, Figure 27-17, Table 27-21 describes smc c/i channel rxbd fields

Serial Management Controllers (SMCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

27-34

Freescale Semiconductor

describes SMC C/I channel RxBD fields.

27.5.8

SMC GCI C/I Channel TxBD

The CP uses this BD, as seen in

, to report about the C/I channel transmit byte.

describes SMC C/I channel TxBD fields.

27.5.9

SMC GCI Event Register (SMCE)/Mask Register (SMCM)

The SMCE generates interrupts and report events recognized by the SMC channel. When an event is

recognized, the SMC sets its corresponding SMCE bit. SMCE bits are cleared by writing ones; writing

zeros has no effect. SMCM has the same bit format as SMCE. Setting an SMCM bit enables, and clearing

an SMCM bit disables, the corresponding interrupt. Unmasked bits must be cleared before the CP clears

0

1

7

8

13

14

15

Offset + 0

E

—

C/I DATA

—

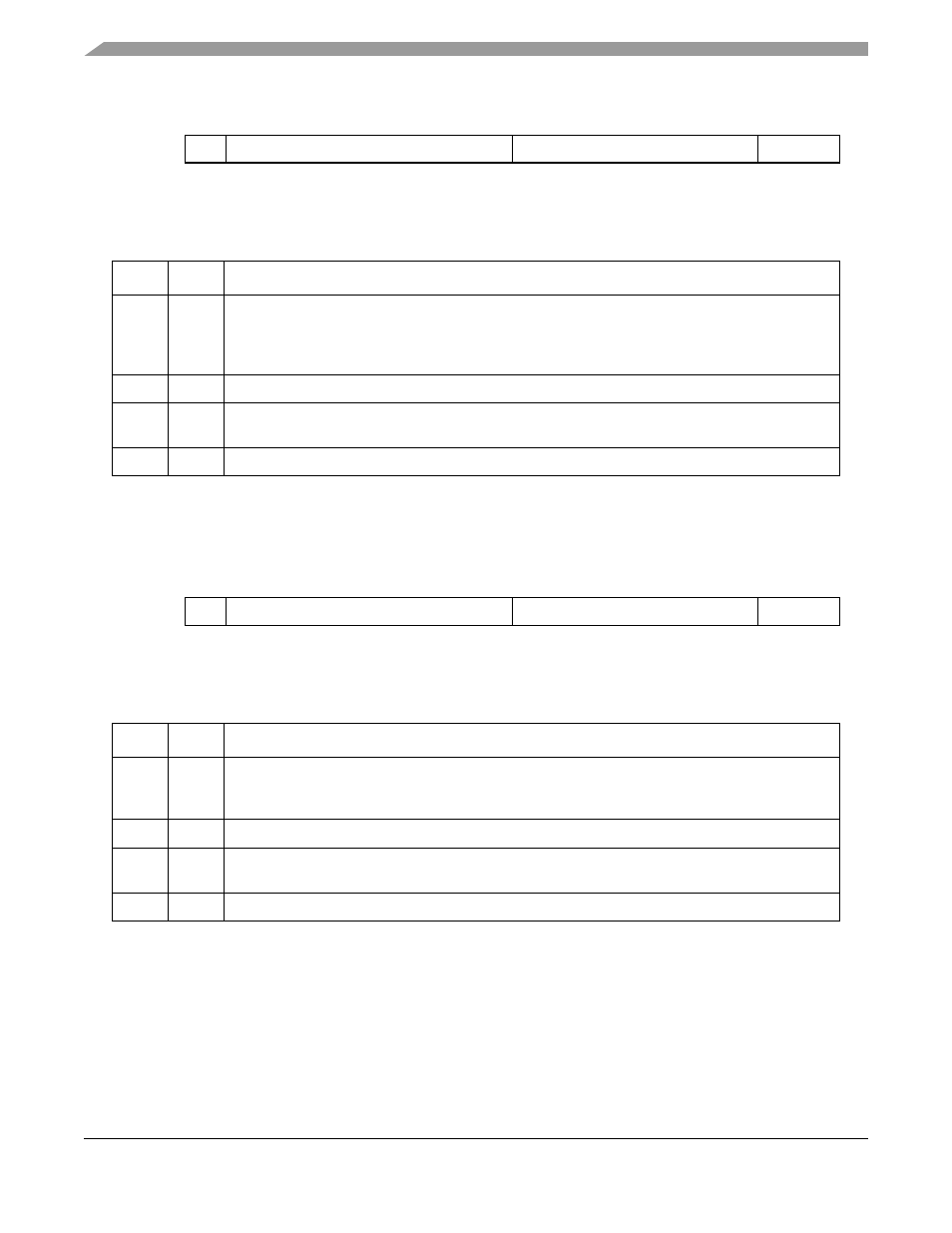

Figure 27-17. SMC C/I Channel RxBD

Table 27-21. SMC C/I Channel RxBD Field Descriptions

Bits

Name

Description

0

E

Empty.

0 Cleared by the CP to indicate that the byte associated with this BD is available to the core.

1 The core sets E to indicate that the byte associated with this BD has been read.

Note that additional data received is discarded until E bit is set.

1–7

—

Reserved, should be cleared.

8–13

C/I

DATA

Command/indication data bits. For C/I channel 0, bits 10–13 contain the 4-bit data field and bits 8–9

are always written with zeros. For C/I channel 1, bits 8–13 contain the 6-bit data field.

14–15

—

Reserved, should be cleared.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Offset + 0

R

—

C/I DATA

—

Figure 27-18. SMC C/I Channel TxBD

Table 27-22. SMC C/I Channel TxBD Field Descriptions

Bits

Name

Description

0

R

Ready.

0 Cleared by the CP after transmission to indicate that the BD is available to the core.

1 Set by the core when data associated with this BD is ready for transmission.

1–7

—

Reserved, should be cleared.

8–13

C/I

DATA

Command/indication data bits. For C/I channel 0, bits 10–13 hold the 4-bit data field (bits 8 and 9

are always written with zeros). For C/I channel 1, bits 8–13 contain the 6-bit data field.

14–15

—

Reserved, should be cleared.