Pci error control capture register (pci_eccr) -41, Pci_eccr field descriptions -41, Figure 9-28 – Freescale Semiconductor MPC8260 User Manual

Page 347: Table 9-15 describes pci_eccr fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-41

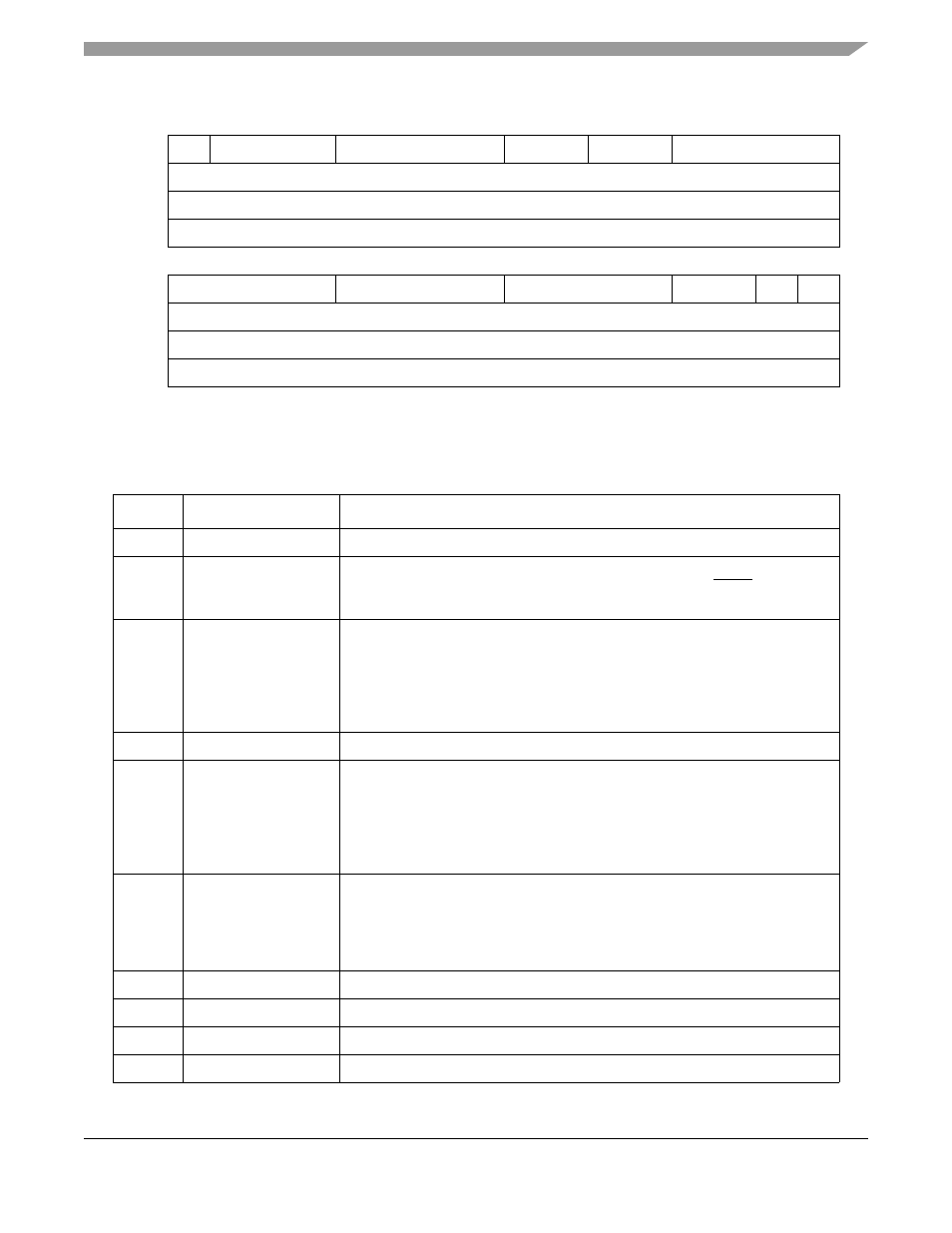

Figure 9-28. PCI Error Control Capture Register (PCI_ECCR)

describes PCI_ECCR fields.

31

30

28

27

24

23

22

21

20

19

16

Field

—

FET

BN

—

TS

ES

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108A2

15

12

11

8

7

4

3

2

1

0

Field

CMD

—

BE

—

PB

VI

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108A0

Table 9-15. PCI_ECCR Field Descriptions

Bits

Name

Description

31

—

Reserved, should be cleared.

30–28

First error type

Type of first PCI error captured. This field is the bit index of the error type in

. For example, a value of 0b101 indicates a PCI SERR received

condition while a value of 0b010 indicates a PCI read data parity error.

27–24

Beat number

32-bit data beat number for data parity error (data parity error only)

0000 1

0001 2

…

0111 8

1000 overflow (transaction larger than one cache line)

23–22

—

Reserved, should be cleared.

21–20

Transaction size

This is the size of the transaction in doublewords (4 bytes) (the PCI bridge as

master only)

00 4 doublewords

01 1 doubleword

10 2 doublewords

11 3 doublewords

19–16

Error source

The source of the PCI transaction

0000 External master

0001 60x master

0101 DMA

All others are reserved.

15–12

Command

PCI command

11–8

—

Reserved, should be cleared.

7–4

Byte enables

PCI byte enables.

3–2

—

Reserved, should be cleared.