Freescale Semiconductor MPC8260 User Manual

Page 592

Serial Interface with Time-Slot Assigner

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

15-16

Freescale Semiconductor

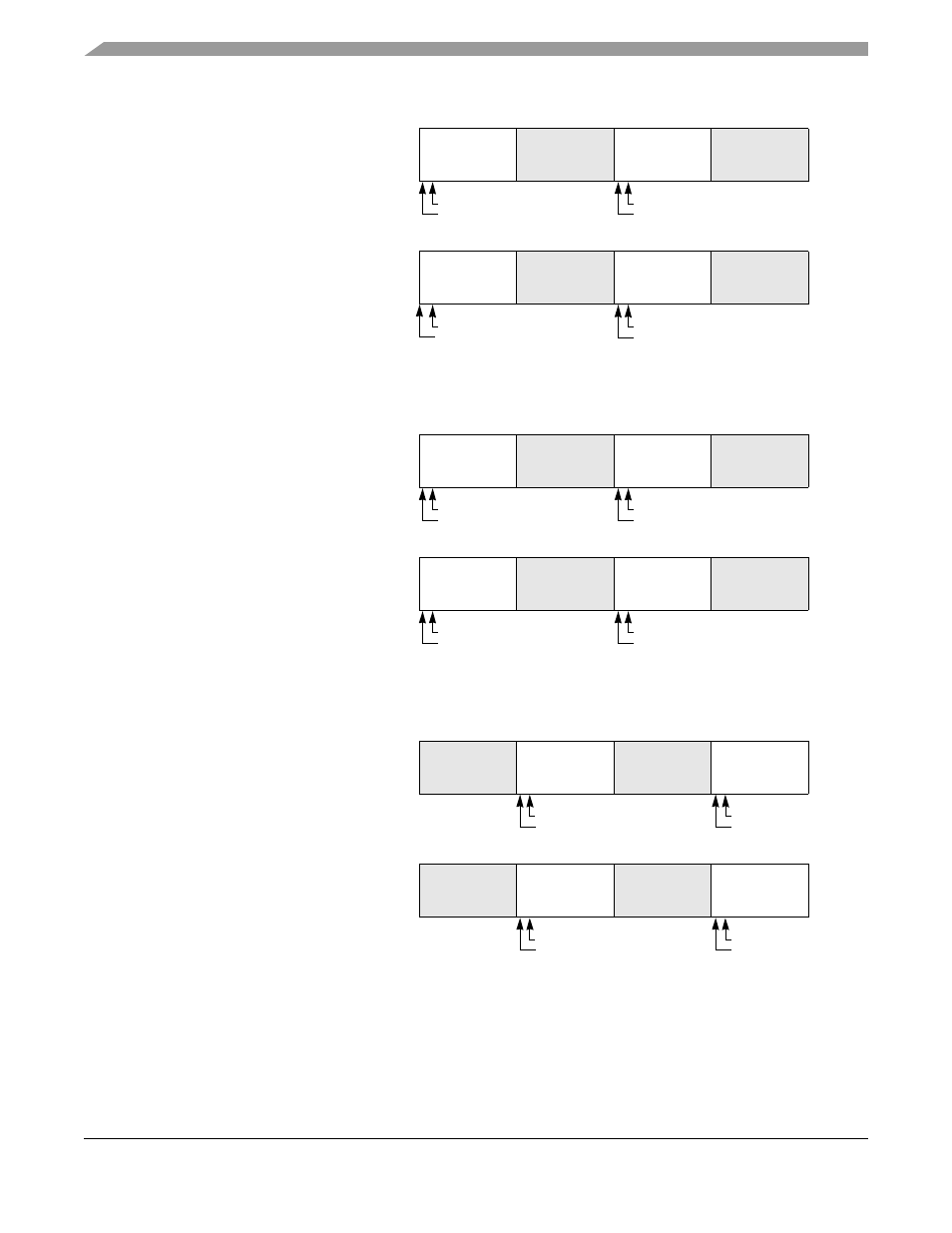

Figure 15-9. Example: SI

x RAM Dynamic Changes, TDMa and b, Same SIx RAM Size

L1TCLKb

L1TSYNCb

64 TXb

Shadow

64 TXa

64 TXb

Route

Route

The TSA uses the first part of

Framing Signals:

L1TCLKa

L1TSYNCa

1)

Initial State

the RAM, and the shadow is

64 TXa

Shadow

0

127 128

255 256

383 384

511

CSRRa=0

The user programs the

2)

Programming

shadow RAM for the new

The SI swaps between

Swap

the shadow and the

Rx and Tx route and sets

the second part of the RAM.

CSR

xn

= 0

current-route RAMs

1024

1151 1152

1279 1280

1407 1408

1535

RAM Address:

CSRTa=0

CSRRb=0

CSRTb=0

CSRRa=1

CSRTa=1

CSRRb=1

CSRTb=1

CSRRa=0

CSRTa=0

CSRRb=0

CSRTb=0

L1RCLKb

L1RSYNCb

64 RXb

Shadow

64 RXa

64 RXb

Route

Route

Framing Signals:

L1RCLKa

L1RSYNCa

64 RXa

Shadow

RAM Address:

CSR

xn

.

L1TCLKb

L1TSYNCb

64 TXb

Shadow

64 TXa

64 TXb

Route

Route

Framing Signals:

L1TCLKa

L1TSYNCa

64 TXa

Shadow

0

127 128

255 256

383 384

511

1024

1151 1152

1279 1280

1407 1408

1535

RAM Address:

L1RCLKb

L1RSYNCb

64 RXb

Shadow

64 RXa

64 RXb

Route

Route

Framing Signals:

L1RCLKa

L1RSYNCa

64 RXa

Shadow

RAM Address:

and resets CSR

xn

.

L1TCLKb

L1TSYNCb

64 TXb

Shadow

64 TXa

64 TXb

Route

Route

Framing Signals:

L1TCLKa

L1TSYNCa

64 TXa

Shadow

0

127 128

255 256

383 384

511

1024

1151 1152

1279 1280

1407 1408

1535

RAM Address:

L1RCLKb

L1RSYNCb

64 RXb

Shadow

64 RXa

64 RXb

Route

Route

Framing Signals:

L1RCLKa

L1RSYNCa

64 RXa

Shadow

RAM Address:

3)