Table 9-49. idr field descriptions, 3 i2o unit, Idr field descriptions -69 – Freescale Semiconductor MPC8260 User Manual

Page 375: Table 9-49, O unit

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-69

9.12.3

I

2

O Unit

The Intelligent Input Output specification (I

2

O) was established in the industry to allow

architecture-independent I/O subsystems to communicate with an OS through an abstraction layer. The

specification is centered around a message passing scheme. An I

2

O embedded peripheral (IOP) is

comprised of memory, processor, and input/output device(s). An IOP dedicates space in its local memory

to hold inbound (from the remote host) and outbound (to the remote host) messages. The space is managed

as memory-mapped FIFOs, with pointers to this memory maintained in hardware.

Messages are made up of frames which are a minimum of 64-bytes in length. The message frame address

(MFA) is the address which points to the first byte of the message frame. The messages are located in

local-system memory. Tracking of the status and location of these messages is done with four FIFOs (two

FIFOs for inbound and two for outbound messages) also located in local-system memory. Hardware

registers inside the PCI bridge’s core logic manage these FIFOs. One FIFO in each queue keeps track of

the free MFAs (Free_LIST FIFO). The other FIFO keeps track of the MFAs which have posted messages

(Post_LIST FIFO).

shows an example of the message queues, although there is no specific

order that these queues must follow.

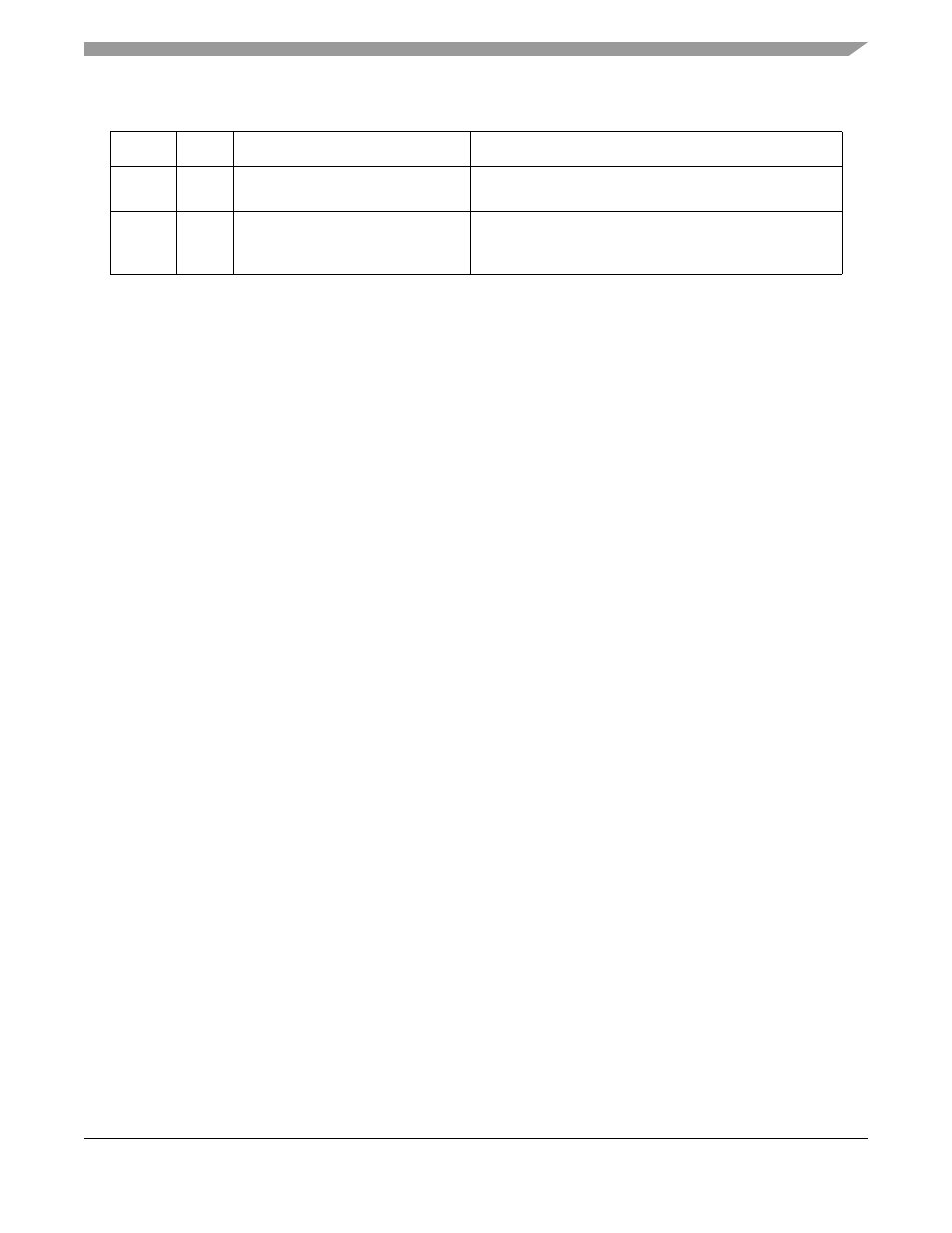

Table 9-49. IDR Field Descriptions

Bits

Name

Access

Description

31

IMC

Write 1 to set from PCI.

Write 1 to clear from local processor.

Machine check. Writing to this bit will generate a machine

check interrupt to the local processor.

30–0

IDR

x

Write 1 to set from PCI.

Write 1 to clear from local processor.

Inbound door bell

x,

where

x

is each bit. Writing a bit in this

register from the PCI bus causes an interrupt to be

generated through

t

he PCI bridge to the local processor.