3 uart baud rate examples, Uart baud rate examples -5, Section 17.3, “uart baud rate examples – Freescale Semiconductor MPC8260 User Manual

Page 635

Baud-Rate Generators (BRGs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

17-5

17.3

UART Baud Rate Examples

For synchronous communication using the internal BRG, the BRGO must not exceed the BRG input clock

divided by 2. Therefore, with a BRG input clock of 66MHz (generated using an external clock source: refer

to BRGCx[EXTC]), the maximum BRGO rate is 33MHz. Program the UART to 16

× oversampling when

using the SCC as a UART. Rates of 8

× and 32× are also available. Assuming 16× oversampling is chosen

in the UART, the maximum data rate is 66 MHz ÷ 16 = 4.125 Mbps. Keeping the above in mind, use the

following formula to calculate the bit rate based on a particular BRG configuration for a UART:

lists typical bit rates of asynchronous communication. Note that here the internal clock rate is

assumed to be 16

× the baud rate; that is, GSMRx_L[TDCR] = GSMRx_L[RDCR] = 0b10.

For synchronous communication, the internal clock is identical to the baud-rate output. To get the preferred

rate, select the system clock according to the following:

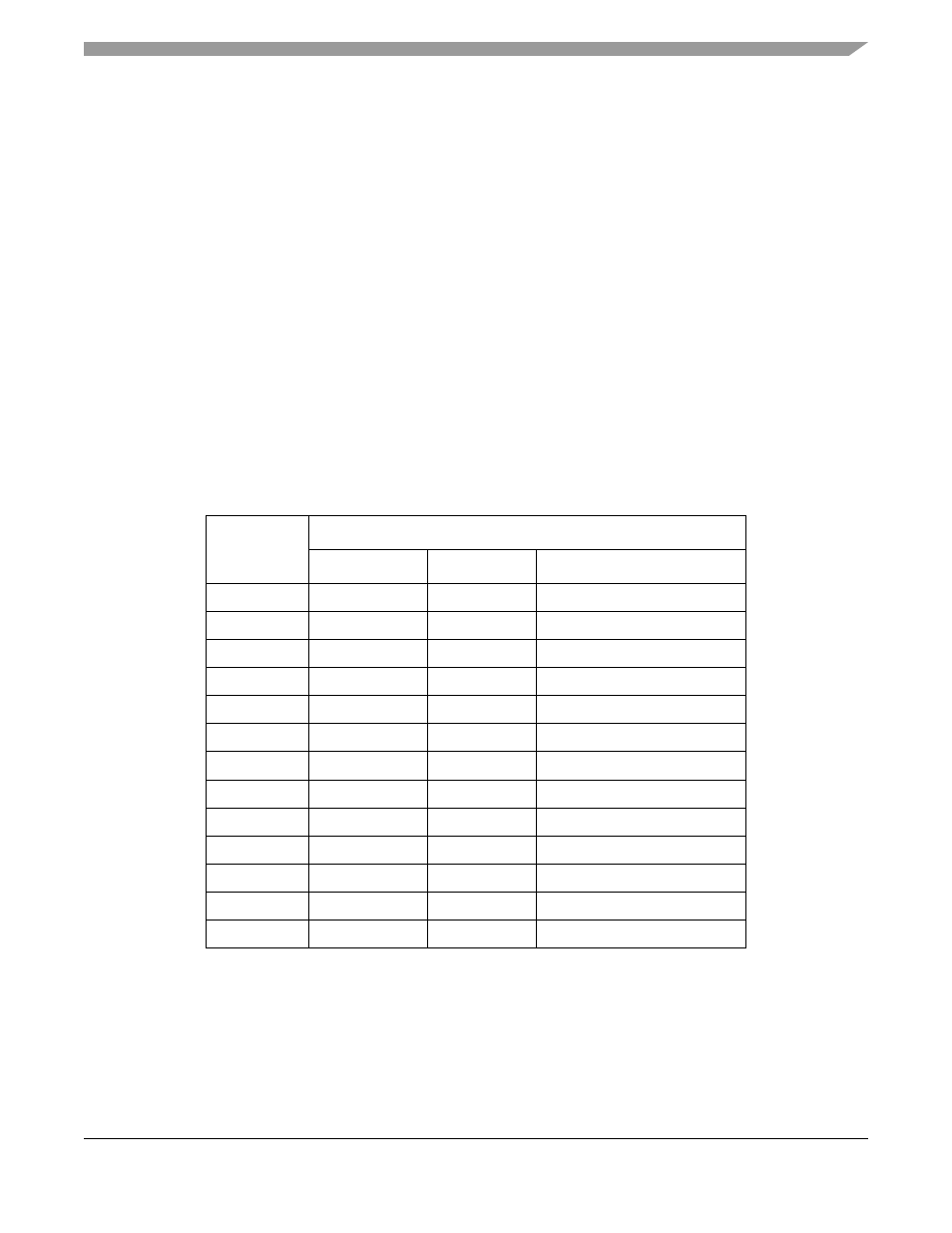

Table 17-3. Typical Baud Rates for Asynchronous Communication

Baud Rate

Using a 66-MHz BRG Input Clock

BRGC

x

[DIV16]

BRGC

x

[CD]

Actual Frequency (Hz)

75

1

3436

75.01

150

1

1718

149.98

300

1

858

300.13

600

1

429

599.56

1200

0

3436

1200.2

2400

0

1718

2399.7

4800

0

858

4802.1

9600

0

429

9593.0

19,200

0

214

19,186

38,400

0

106

38,551

57,600

0

71

57,292

115,200

0

35

114,583

460,000

0

8

458,333

Async Baud Rate

BRGCLK or External Clock Source

Prescale Divider

(

)

Clock Divider + 1

(

)

Sampling Rate

(

)

•

•

-------------------------------------------------------------------------------------------------------------------------------------------------

=

BRGCx[EXTC]

BRGCx[DIV16]

(

)

BRGCx[CD] + 1

(

)

GSMRx_L[xDCR]

(

)

•

•

---------------------------------------------------------------------------------------------------------------------------------------------------------

=

Sync Baud Rate

BRGCLK or External Clock Source

Prescale Divider

(

)

Clock Divider + 1

(

)

•

--------------------------------------------------------------------------------------------------

=