Freescale Semiconductor MPC8260 User Manual

Page 1246

FCC Transparent Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

37-4

Freescale Semiconductor

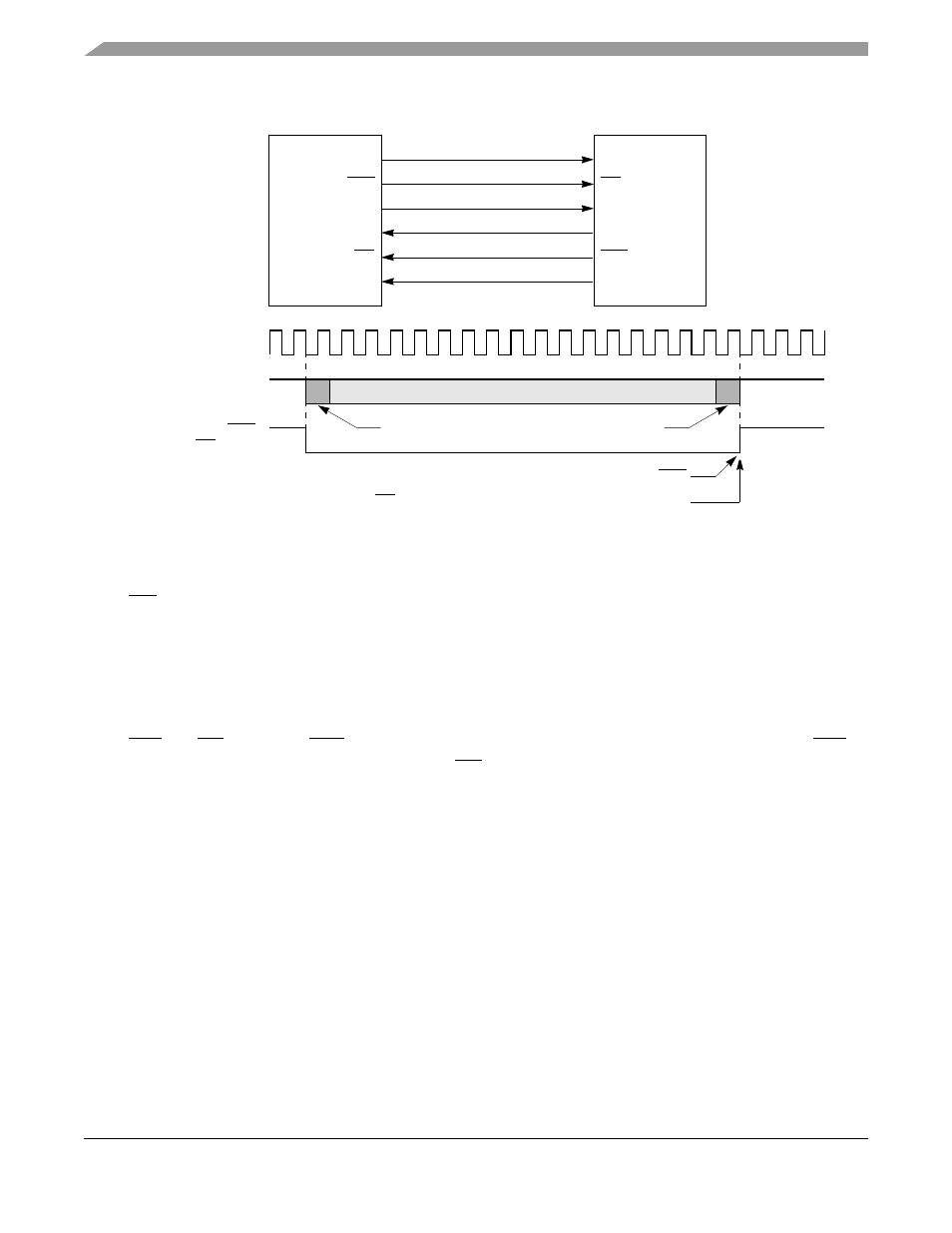

Figure 37-2. Sending Transparent Frames between PowerQUICC IIs

PowerQUICC II(A) and PowerQUICC II(B) exchange transparent frames and synchronize each other

using RTS and CD. However, CTS is not required because transmission begins at any time. Thus, RTS is

connected directly to the other PowerQUICC II’s CD. GFMR[SYNL] is not used and transmission and

reception from each PowerQUICC II are independent.

RXD

CD

CLKx

TXD

RTS

CD

RXD

BRGOx

RTS

TXD

CLKx

BRGOx

BRGOx

Last Bit of Frame Data

First Bit of Frame Data

(Output is CLKx Input)

TXD

(Output is RXD Input)

RTS

(Output is CD Input)

or CRC

TxBD[L] = 1 Causes Negation of RTS

CD Lost Condition Terminates Reception of Frame

PowerQUICC II (A)

PowerQUICC II (B)

Notes:

1

Each PowerQUICC II generates its own transmit clocks. If the transmit and receive clocks are the same, one can

generate transmit and receive clocks for the other PowerQUICC II. For example, CLKx on PowerQUICC II (B) could

be used to clock the transmitter and receiver

2

CTS should be configured as always asserted in the parallel I/O port or connected to ground externally.

3

The required GSMR configurations are DIAG= 00, CTSS=1, CTSP is a don’t care, CDS=1, CDP=0, TTX=1, and

TRX=1. REVD and TCRC are application-dependent.

4

The transparent frame contains a CRC if TxBD[TC] is set.