Figure 11-56. ram array indexing, Table 11-35. upm routines start addresses, Ram array indexing -65 – Freescale Semiconductor MPC8260 User Manual

Page 483: Upm routines start addresses -65

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

11-65

•

Read burst cycle pattern (RBS)

•

Write single-beat pattern (WSS)

•

Write burst cycle pattern (WBS)

These patterns are described in

Section 11.6.1.1, “Memory Access Requests.”

A UPM refresh timer request pattern initiates a refresh timer pattern (PTS), as described in

Section 11.6.1.2, “UPM Refresh Timer Requests.”

An exception (caused by a soft reset or the assertion of TEA) occurring while another UPM pattern is

running initiates an exception condition pattern (EXS).

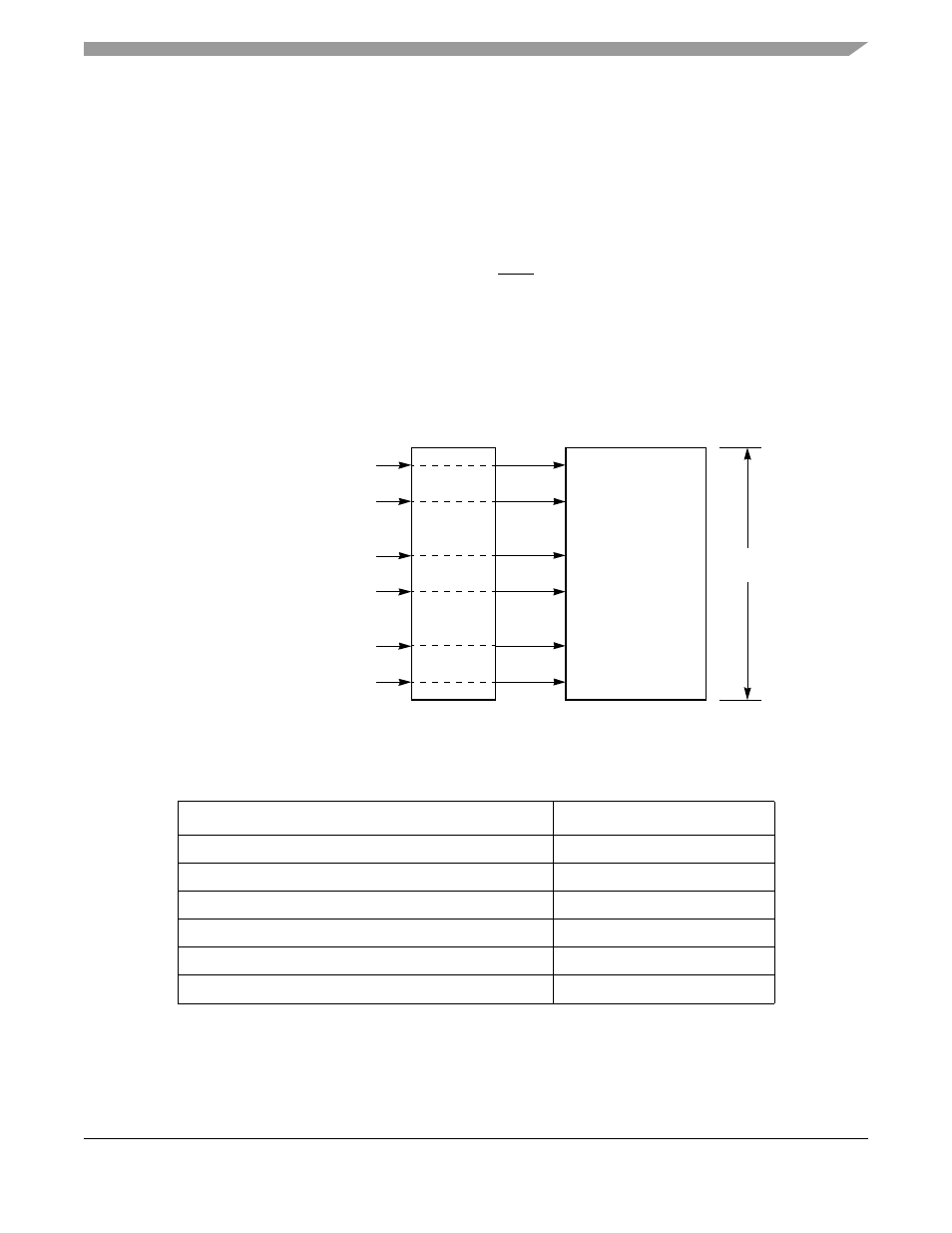

A special pattern in the RAM array is associated with each of these cycle type.

shows the

start addresses of these patterns in the UPM RAM, according to cycle type.

RUN

commands (MxMR[OP]

= 11), however, can initiate patterns starting at any of the 64 UPM RAM words.

Figure 11-56. RAM Array Indexing

show the start address of each pattern.

Table 11-35. UPM Routines Start Addresses

UPM Routine

Routine Start Address

Read single-beat (RSS)

0x00

Read burst (RBS)

0x08

Write single-beat (WSS)

0x18

Write burst (WBS)

0x20

Refresh timer (PTS)

0x30

Exception condition (EXS)

0x3C

Write Single-Beat Request

Read Burst Request

Read Single-Beat Request

Write Burst Request

RAM Array

Refresh Timer Request

Exception Condition Request

RSS

RBS

WSS

WBS

PTS

EXS

64 RAM

Words

Array Index

Generator