Table 9-1. pci terminology, 1 pci interface operation, 1 bus commands – Freescale Semiconductor MPC8260 User Manual

Page 312: Pci interface operation -6, Bus commands -6, Pci terminology -6

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-6

Freescale Semiconductor

•

Address translation units for address mapping between host and agent.

Efforts were made to keep the terminology in this chapter consistent with the PCI Specification, revision

2.2, and other PCI documentation; therefore, the terms found in

may differ from most

documentation for processors that implement the PowerPC architecture (for example, architecture

specification or reference manuals).

NOTE: PCI Bridge Signal Naming

PCI bridge signals are defined in most cases with the prefix “PCI_” (for

example, PCI_IRDY—see

). In this chapter, however, the prefix

is not used. For descriptions of PCI bridge signals, refer to

9.9.1

PCI Interface Operation

The following sections discuss the operation of the PCI bus.

9.9.1.1

Bus Commands

PCI bus commands indicate the type of transaction occurring on the bus. These commands are encoded on

PCI_C/BE[3-0] during the address phase of the transaction. PCI bus commands are described in

.

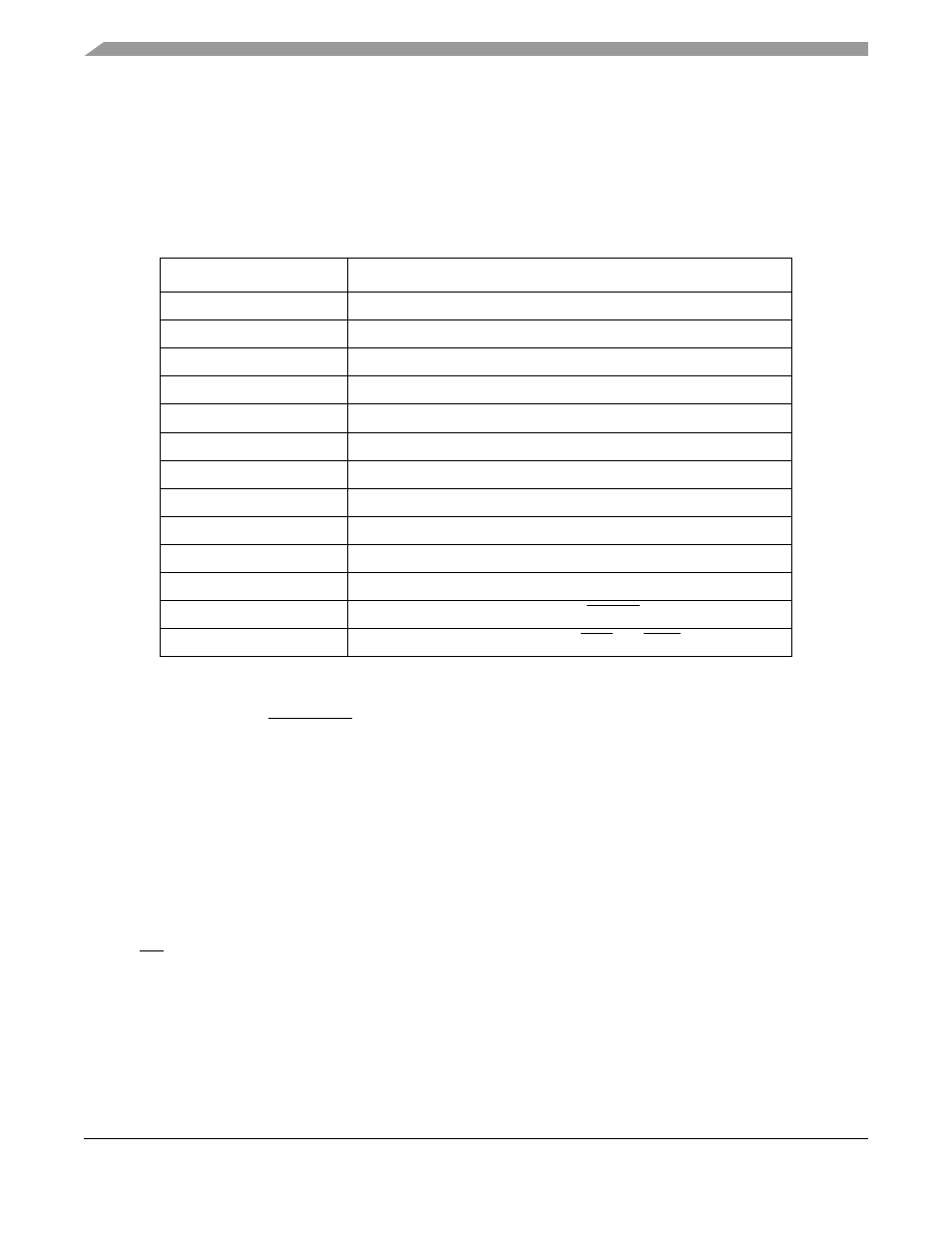

Table 9-1. PCI Terminology

Term

Definition

LSB/Lower Order

Represents bit 0 or the bits closest to the LSB

MSB/High Order

Represents bit 31 or the bits closest to the MSB

Byte

Represents 8 bits of information

Word

Represents 16 bits or 2 bytes

Double-Word

Represents 32 bits or 2 words or 4 bytes

Quad-Word

Represents 64 bits or 2 double-words or 4 words or 8 bytes

Beat

Represents any valid data during a data transfer

Burst

Represents any 1 or more beat transfers

Edge/Clock Edge

Represents the rising edge of the PCI clock

Cycle/Clock Cycle

Represents the time period between clock edges

Asserted/Negated

Represents the globally visible state of the signal on the clock edge

Address Phase

Represents the first clock cycle where FRAME is asserted

Data Phase(s)

Represents the clock cycle(s) where IRDY and TRDY are asserted