1 scc, fcc, and mcc relative priority, Scc, fcc, and mcc relative priority -12 – Freescale Semiconductor MPC8260 User Manual

Page 184

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-12

Freescale Semiconductor

Notice the lack of SDMA interrupt sources, which are reported through each individual FCC, SCC, SMC,

SPI, or I

2

C channel. The only true SDMA interrupt source is the SDMA channel bus error entry that is

reported when a bus error occurs during an SDMA access. There are two ways to add flexibility to the table

of CPM interrupt priorities—the FCC, MCC, and SCC relative priority option, described in

Section 4.2.2.1, “SCC, FCC, and MCC Relative Priority,”

and the highest priority option, described in

Section 4.2.2.3, “Highest Priority Interrupt.”

4.2.2.1

SCC, FCC, and MCC Relative Priority

The relative priority between the four SCCs, three FCCs, and MCC is programmable and can be changed

dynamically. In

there is no entry for SCC1–SCC4, MCC1–MCC2, FCC1–FCC3, but rather there

are entries for XCC1–XCC8 and YCC1–YCC8. Each SCC can be mapped to any YCC location and each

FCC and MCC can be mapped to any XCC location. The SCC, FCC, and MCC priorities are programmed

in the CPM interrupt priority registers (SCPRR_H and SCPRR_L) and can be changed dynamically to

implement a rotating priority.

In addition, the grouping of the locations of the YCC entries has the following two options

•

Group. In the group scheme, all SCCs are grouped together at the top of the priority table, ahead

of most other CPM interrupt sources. This scheme is ideal for applications where all SCCs, FCCs,

and MCCs function at a very high data rate and interrupt latency is very important.

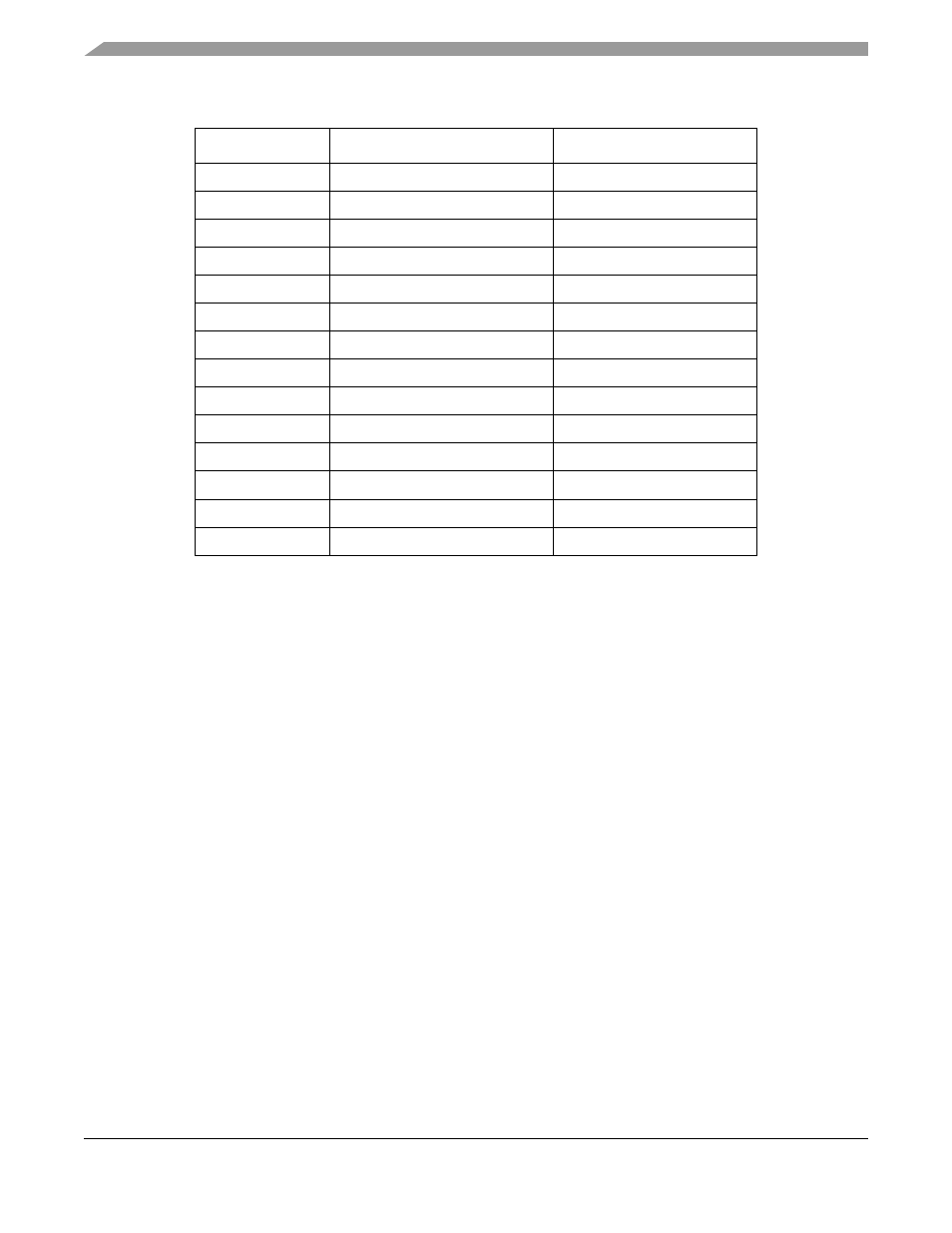

60

Parallel I/O–PC4

No

61

XSIU7 (GSIU = 1)

No (TMCNT,PIT,PCI

1

= Yes)

62

IDMA4

Yes

63

SPI

Yes

64

Parallel I/O–PC3

No

65

Parallel I/O–PC2

No

66

SMC1

Yes

67

YCC7 (spread)

Yes

68

SMC2

Yes

69

Parallel I/O–PC1

No

70

Parallel I/O–PC0

No

71

XSIU8 (GSIU = 1)

No (TMCNT,PIT,PCI

1

= Yes)

72

YCC8(spread)

Yes

73

Reserved

—

1

MPC8250, MPC8265, and MPC8266 only

Table 4-2. Interrupt Source Priority Levels (continued)

Priority Level

Interrupt Source Description

Multiple Events