13 partial data valid indication (psdval), Partial data valid indication (psdval) -11 – Freescale Semiconductor MPC8260 User Manual

Page 429

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

11-11

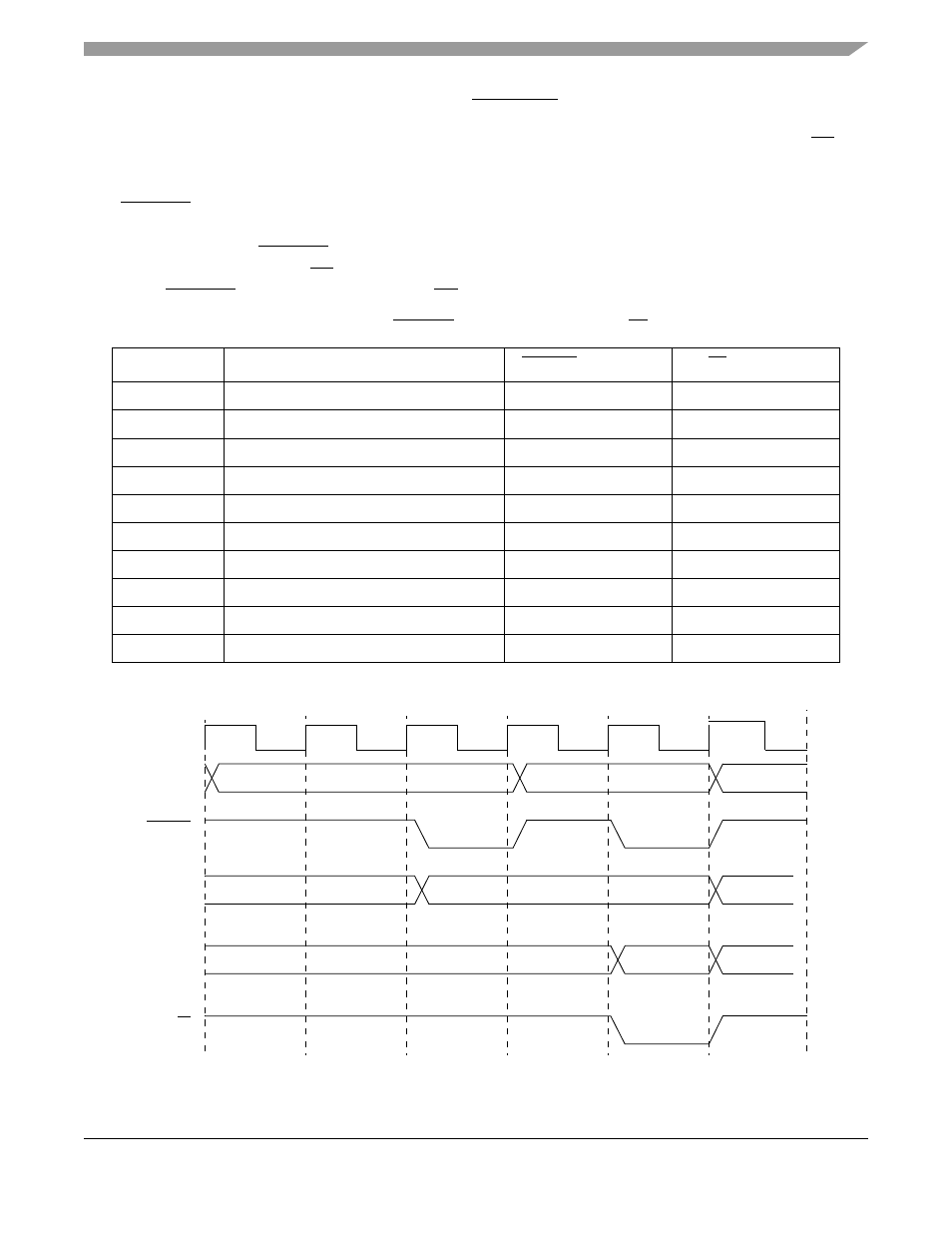

11.2.13 Partial Data Valid Indication (PSDVAL)

The 60x and local buses have an internal 64-bit data bus. According to the 60x bus specification, TA is

asserted when up to a double word of data is transferred. Because the PowerQUICC II supports memories

with port sizes smaller than 64 bits, there is a need for partial data valid indication. The memory controller

uses PSDVAL to indicate that data is latched by the memory on write accesses or valid data is present on

read accesses. The quantity of the data depends on the memory port size and the transfer size. The memory

controller accumulates PSDVAL assertions, and when a double word (or the transfer size) is transferred,

the memory controller asserts TA to indicate that a 60x data beat was transferred.

shows the

number of PSDVAL assertions needed for one TA assertion under various circumstances.

shows a double-word transfer on 32-bit port size memory.

Figure 11-5. Partial Data Valid for 32-Bit Port Size Memory, Double-Word Transfer

Table 11-1. Number of PSDVAL Assertions Needed for TA Assertion

Port Size

Transfer Size

PSDVAL Assertions

TA Assertions

64

Any

1

1

32

Double word

2

1

32

Word/half word/byte (32-bit aligned)

1

1

16

Double Word

4

1

16

Word

2

1

16

Half/byte

1

1

8

Double word

8

1

8

Word

4

1

8

Half

2

1

8

Byte

1

1

Clock

External

PSDVAL

Internal

TA

Data Bus

Data Bus

(32 msb)

(32 msb)

Upper 4 bytes

Lower 4 bytes

Internal

Data Bus

(32 lsb)

Upper 4 bytes

Lower 4 bytes