Figure 30-55. interrupt queue structure, 2 interrupt queue entry, Figure 30-56. interrupt queue entry – Freescale Semiconductor MPC8260 User Manual

Page 1002: Interrupt queue entry -82, Interrupt queue structure -82, Section 30.11.2, “interrupt queue entry

ATM Controller and AAL0, AAL1, and AAL5

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

30-82

Freescale Semiconductor

the queue. If the CP tries to overwrite a valid entry (V = 1), an overflow condition occurs and the queue’s

overflow flag, FCCE[INTOx], is set.

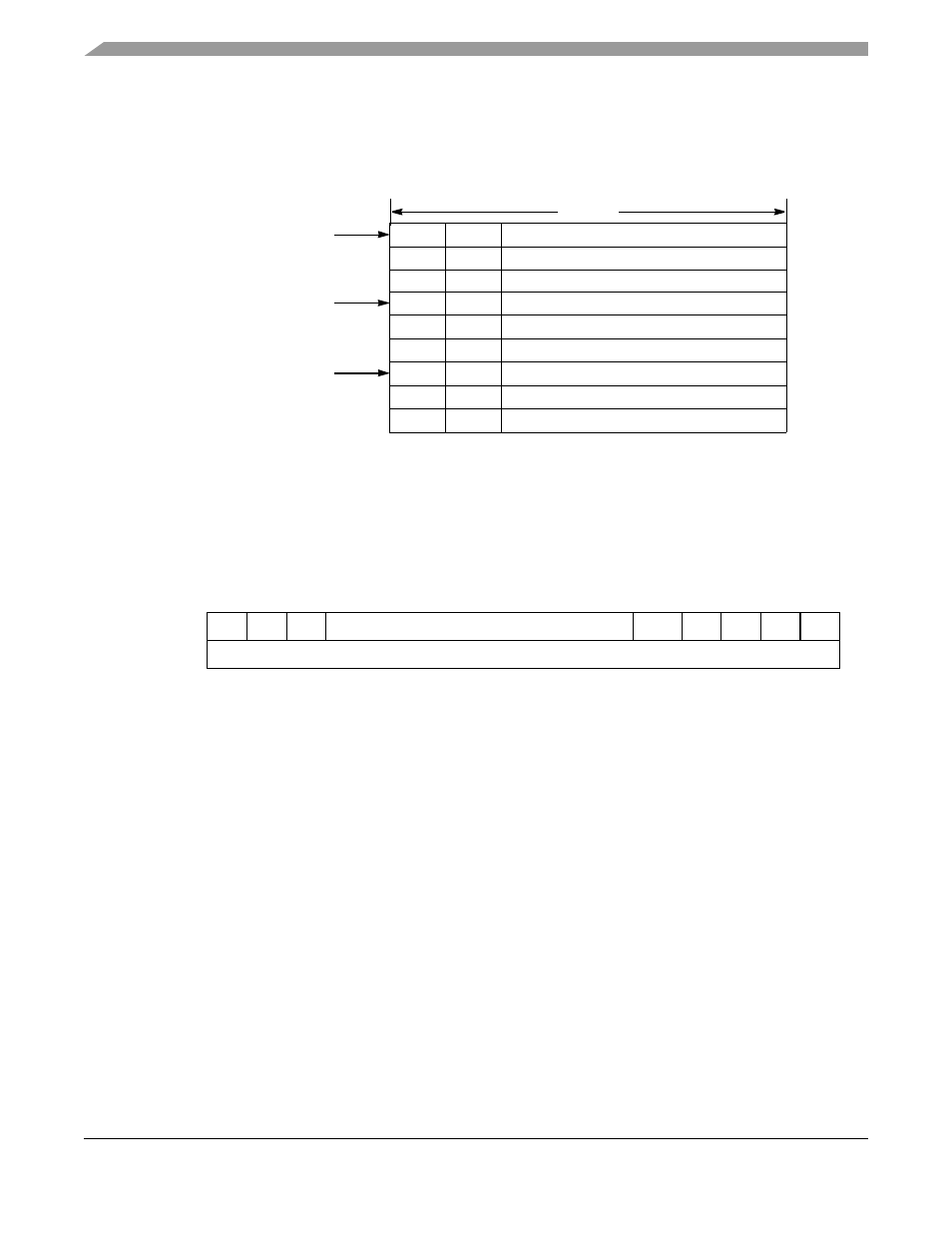

The interrupt queue structure is displayed in

.

Figure 30-55. Interrupt Queue Structure

30.11.2 Interrupt Queue Entry

Each one-word interrupt queue entry provides detailed interrupt information to the host.

shows an entry.

describes interrupt queue entry fields.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Offset + 0x00

V

—

W

—

TBNR RXF BSY TXB RXB

Offset + 0x02

Channel Code (CC)

Figure 30-56. Interrupt Queue Entry

V = 0

W = 0

Invalid

V = 0

W = 0

Invalid

V = 0

W = 0

Invalid

V = 1

W = 0

Interrupt Entry

V = 1

W = 0

Interrupt Entry

V = 1

W = 0

Interrupt Entry

V = 0

W = 0

Invalid

V = 0

W = 0

Invalid

V = 0

W = 1

Invalid

INTQ_BASE

Software (Core) Pointer

INTQ_PTR

Word