Figure 9-36. pci bus status register, Table 9-23. pci bus status register description, 5 revision id register – Freescale Semiconductor MPC8260 User Manual

Page 355: Revision id register -49, Pci bus status register -49, Pci bus status register description -49

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-49

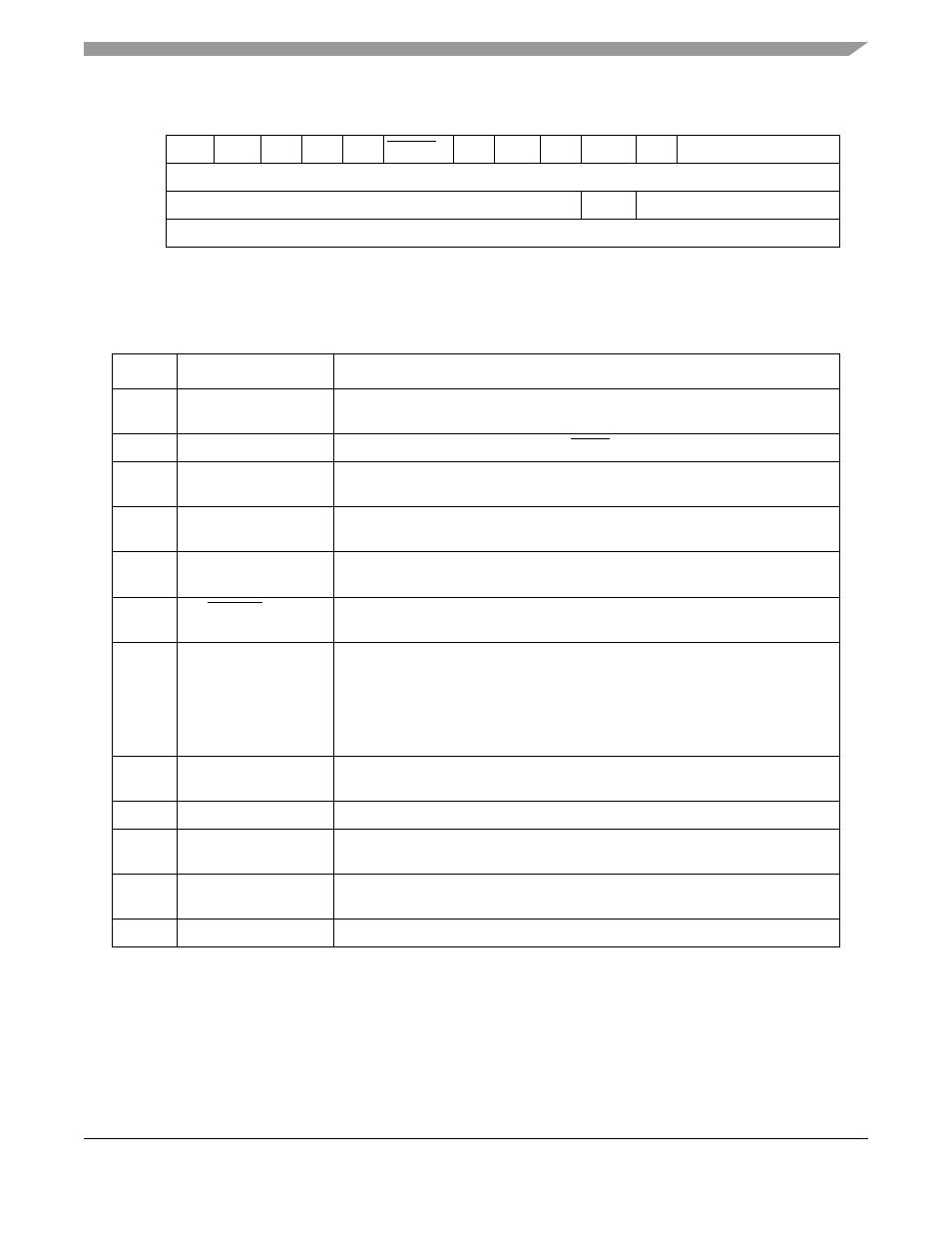

Figure 9-36. PCI Bus Status Register

Table 9-23. describes the PCI bus status register fields.

9.11.2.5

Revision ID Register

describe the revision ID register.

15

14

13

12

11

10

9

8

7

6

5

4

3

0

Field DPERR SSERR RM-A RT-A ST-A DEVSEL_T DPD FB-BC

—

66MHzC

CL

—

Reset

0000_0000_1011_0000

R/W

R/W

R

R/W

Addr

0x06

Table 9-23. PCI Bus Status Register Description

Bits

Name

Description

15

Detected parity error

Set whenever the PCI bridge

detects a parity error on the PCI bus, even if parity

error handling is disabled (as controlled by bit 6 in the PCI bus command register).

14

Signaled system error

Set whenever the PCI bridge asserts SERR on the PCI bus.

13

Received master-abort Set whenever the PCI bridge, acting as the PCI master on the PCI bus, terminates

a transaction (except for a special-cycle) using master-abort.

12

Received target-abort

Set whenever a PCI bridge-initiated transaction on the PCI bus is terminated by

a target-abort.

11

Signaled target-abort

Set whenever the PCI bridge, acting as the PCI target on the PCI bus, issues a

target-abort to a PCI master.

10–9

DEVSEL timing

Hardwired to 0b00, indicating that the PCI bridge uses fast device-select timing

on the PCI bus.

8

Data parity detected

Set upon detecting a data parity error on the PCI bus. Three conditions must be

met for this bit to be set:

• The PCI bridge detects a parity error.

• The PCI bridge is acting as the bus master for the operation in which the error

occurred.

• Bit 6 in the PCI bus command register is set.

7

Fast back-to-back

capable

Hardwired to 1, indicating that the PCI bridge as a target is capable of accepting

fast back-to-back transactions.

6

—

Reserved, should be cleared.

5

66-MHz capable

This bit is read-only and indicates that the PCI bridge is capable of 66-MHz PCI

bus operation on the PCI bus.

4

Capabilities List

Hardwired to

1

, indicating that the PCI bridge implements new capabilities on the

PCI bus.

3–0

—

Reserved, should be cleared.