Table 9-16. pitarx field descriptions, 16 pci inbound base address registers (pibarx), Pci inbound base address registers (pibarx) -42 – Freescale Semiconductor MPC8260 User Manual

Page 348: Pitarx field descriptions -42, 16 pci inbound base address registers (pibar x), Table 9-16. describes pitar x

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-42

Freescale Semiconductor

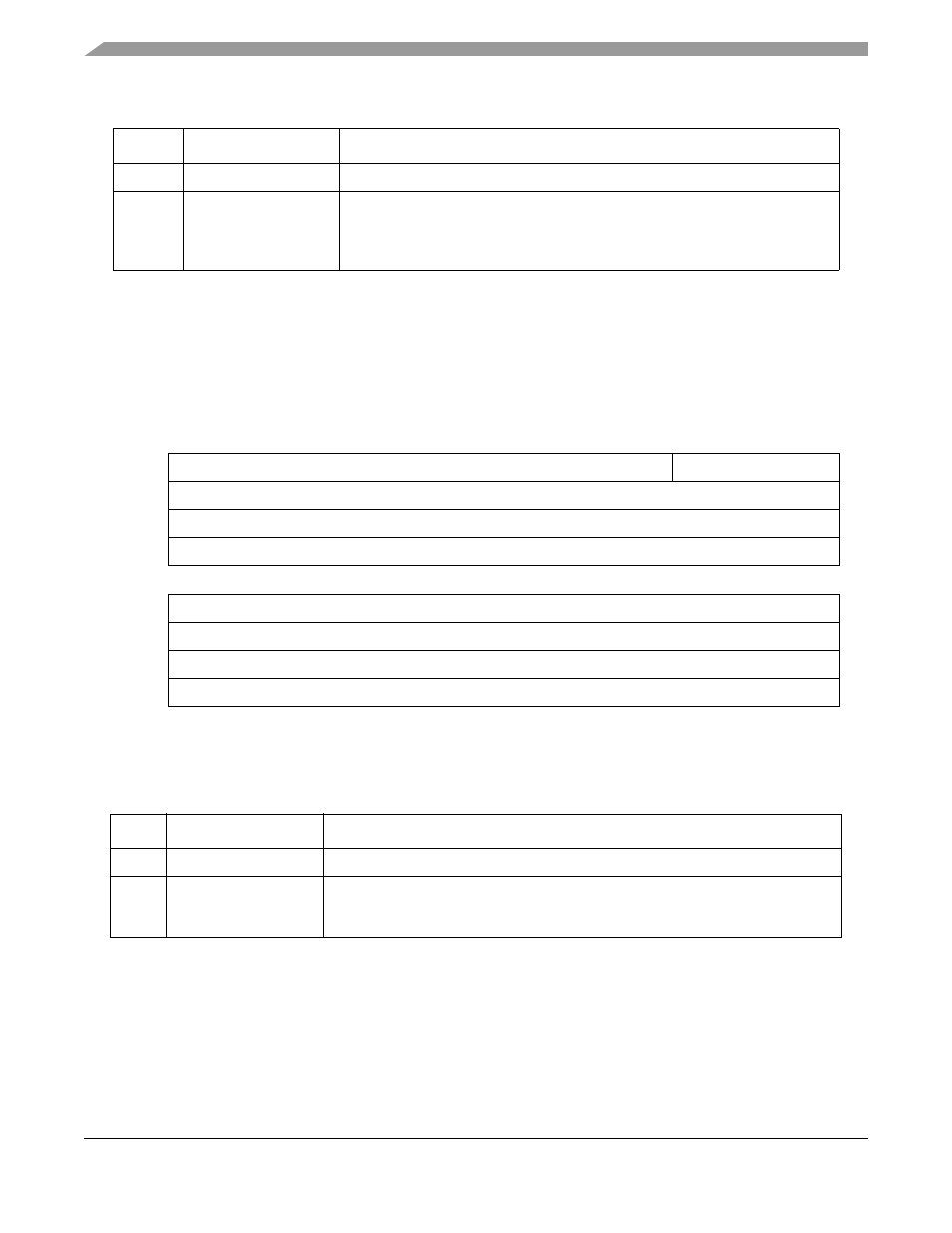

9.11.1.15 PCI Inbound Translation Address Registers (PITAR

x)

The PCI inbound translation address registers (PITARx), shown in

, select the base addresses

in the 60x address space of the translation windows for transactions generated by the master on the PCI

bus. The new translated address is created by concatenating the transaction offset to this base address.

Refer to

Section 9.10.2.1, “PCI Inbound Translation.”

Figure 9-29. PCI Inbound Translation Address Registers (PITAR

x)

Table 9-16. describes PITARx.

9.11.1.16 PCI Inbound Base Address Registers (PIBAR

x)

The PCI inbound base address registers (PIBARx), shown in

, select the starting addresses (in

PCI memory space)

of the windows to be translated. These registers are tied to the GPLABARx registers;

Section 9.11.2.14, “General Purpose Local Access Base Address Registers (GPLABARx).”

A change

1

Parity bit

Parity bit for PCI bus data word.

0

Valid info

When this bit is set, the PCI bus error capture registers (PCI_EACR, PCI_EDCR,

and PCI_ECCR) contain valid information.

Writing ‘0’ to this bit enables the capture of a new error in the PCI bus error

capture registers (PCI_EACR, PCI_EDCR, and PCI_ECCR).

31

20

19

16

Field

—

TA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108EC (PITAR0); 0x108D2 (PITAR1)

15

0

Field

TA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108EA (PITAR0); 0x108D0 (PITAR1)

Table 9-16. PITAR

x Field Descriptions

Bits

Name

Description

31–20

—

Reserved, should be cleared.

19–0

Translation Address

60x address which indicates the starting point of the inbound translated address.

The translation address must be aligned based on the window’s size. This

corresponds to bits 31-12 of a 32-bit address

Table 9-15. PCI_ECCR Field Descriptions (continued)

Bits

Name

Description