Freescale Semiconductor MPC8260 User Manual

Page 1099

ATM AAL2

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

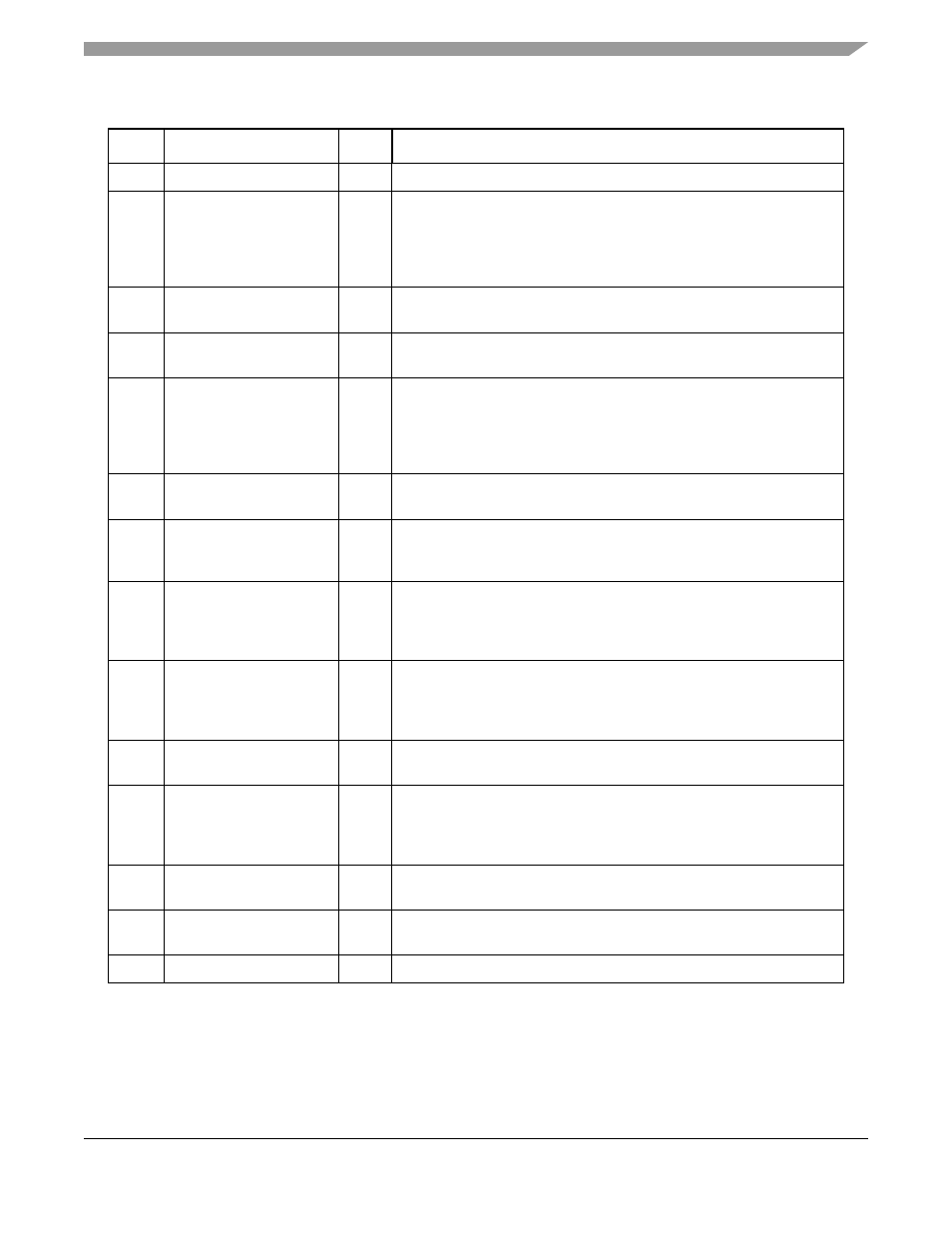

32-37

0xA4

EPAYLOAD

Word

Reserved payload. Initialize to 0x6A6A6A6A.

0xA8

Trm

Word

(ABR only) The upper bound on the time between F-RM cells for an

active source. TM 4.0 defines the Trm period as 100 msec. The Trm value

is defined by the system clock and the time stamp timer prescaler (See

RTSCR). For time stamp prescalar of 1µs, Trm should be set to 100

ms/1µs = 100,000.

0xAC

Nrm

Hword

(ABR only) Controls the maximum cells the source may send for each

F-RM cell. Set to 32 cells.

0xAE

Mrm

Hword

(ABR only) Controls the bandwidth between F-RM, B-RM and user data

cell. Set to 2 cells.

0xB0

TCR

Hword

(ABR only) Tag cell rate. The minimum cell rate allowed for all ABR

channels. An ABR channel whose ACR is less than TCR sends only

out-of-rate F-RM cells at TCR. Should be set to 10 cells/sec as defined

in the TM 4.0. Uses the ATMF TM 4.0 floating-point format. Note that the

APC minimum cell rate should be at least TCR.

0xB2

ABR_RX_TCTE

Hword

(ABR only) Points to total of 16 bytes reserved dual-port RAM area used

by the CP. Should be 16-byte aligned. User-defined.

0xB4

RxQD_Base_Ext

Word

Points to the base address of the external RxQD table. The actual

address of the first RxQD in the table is RxQD_Base_Ext + 512*4.

User-defined.

0xB8

RX_UDC_Base

Word

Valid only for AAL2 VCs. Points to the base of the RX UDC header table

that contains the UDC headers of the AAL2 VCs. The pointer to a VC

UDC header is: RX_UDC_Base + 16*CH# (where CH# is the ATM

channel number)

0xBC

TX_UDC_Base

Word

Valid only for AAL2 VCs. Points to the base of the TX UDC header table

that contains the UDC headers of the AAL2 VCs. The pointer to a VC

UDC header is: TX_UDC_Base + 16*CH# (where CH# is the ATM

channel number)

0xC0–

0xDF

—

—

Reserved. Should be cleared during initialization.

0xE0

TCELL_TMP_BASE_EXT

Word

Transmit Cell Temporary base address. Points to a total of

64*last_AAL2_Ch# octets reserved in external memory for partially filled

cells. Note: TCELL_TMP_BASE_EXT must be on the same bus as the

all the AAL2 data buffers required for CPS, SSSAR and CID switching.

0xE4–

0xFB

—

—

Reserved. Should be cleared during initialization.

0xFC

PAD_TMP_BASE

Hword

PAD template base address. Points to an internal memory area that

contains the zero cell template. Should be 64-byte aligned. User-defined.

0xFE

—

—

Reserved. Should be cleared during initialization.

Table 32-13. AAL2 Parameter RAM (continued)

Offset

Name

Width

Description