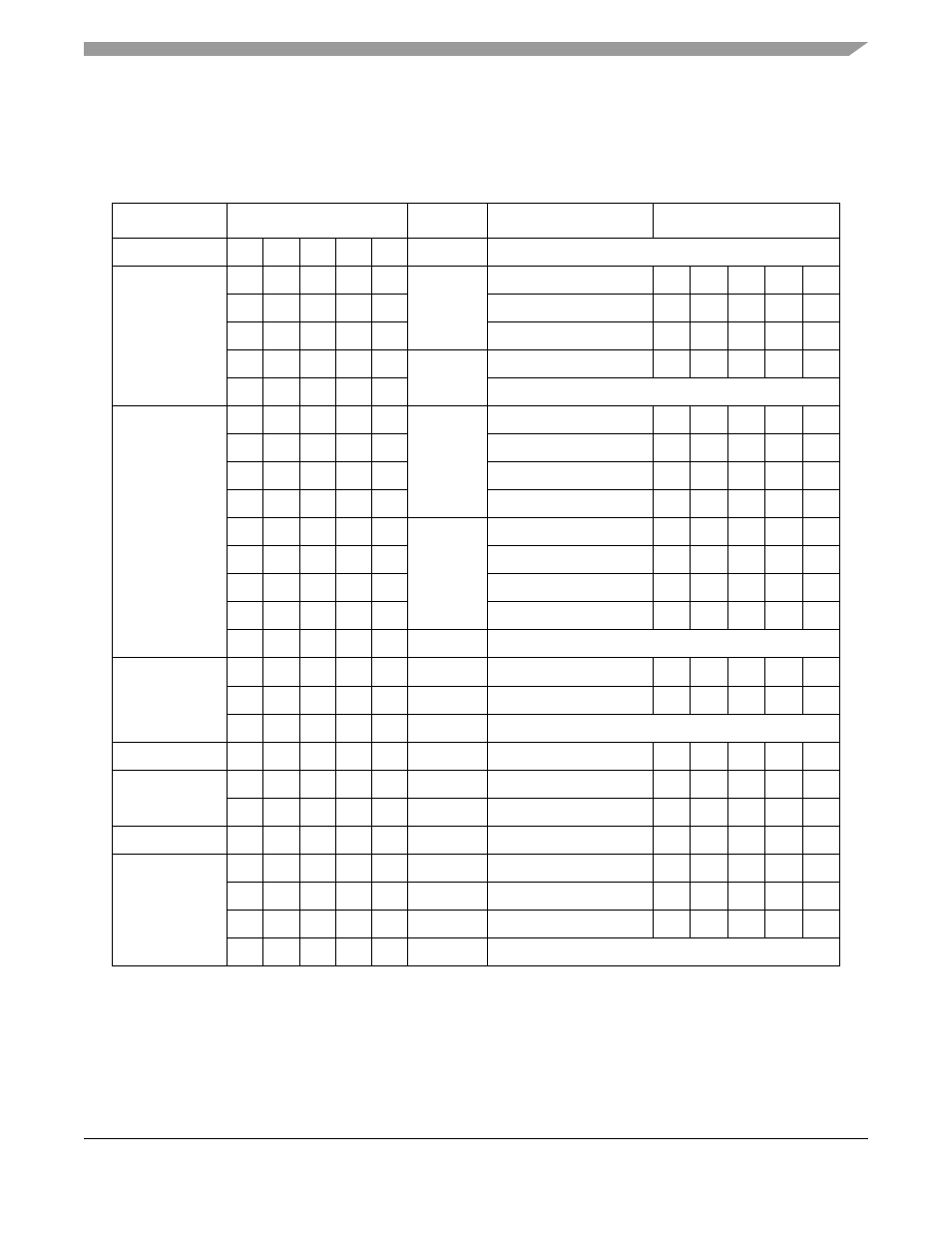

Table 8-9. address and size state calculations, 8 extended transfer mode, Extended transfer mode -19 – Freescale Semiconductor MPC8260 User Manual

Page 293: Address and size state calculations -19, Table 8-9

The 60x Bus

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

8-19

calculation state machine. Note that the address and size states are for internal use and are not transferred

on the address or TSIZ pins. Extended transactions (16- and 24-byte) are not described here but can be

determined by extending this table for 9-, 10-, 16-, 23-, and 24-byte transactions.

8.4.3.8

Extended Transfer Mode

The PowerQUICC II supports an extended transfer mode that improves bus performance. This should not

be confused with the extended bus protocol used to support direct-store operations supported in some

earlier processors that implement the PowerPC architecture. The PowerQUICC II can generate 5-, 6-, 7-,

Table 8-9. Address and Size State Calculations

Size State

Address State [0–4]

Port Size

Next Size State

Next Address State [0–4]

Byte

x

x

x

x

x

x

Stop

2-Byte

x

x

x

x

0

Byte

Byte

x

x

x

x

1

x

x

0

0

1

Byte

x

x

0

1

0

x

x

1

0

1

Byte

x

x

1

1

0

x

x

x

0

1

Half

Byte

x

x

x

1

0

x

x

x

x

0

Stop

3-Byte

x

x

0

0

0

Byte

2-Byte

x

x

0

0

1

x

x

0

0

1

2-Byte

x

x

0

1

0

x

x

1

0

0

2-Byte

x

x

1

0

1

x

x

1

0

1

2-Byte

x

x

1

1

0

x

x

0

0

0

Half

Byte

x

x

0

1

0

x

x

0

0

1

2-Byte

x

x

0

1

0

x

x

1

0

0

Byte

x

x

1

1

0

x

x

1

0

1

2-Byte

x

x

1

1

0

x

x

x

x

x

Word

Stop

4-Byte

x

x

x

0

0

Byte

3-Byte

x

x

x

0

1

x

x

x

0

0

Half

2-Byte

x

x

x

1

0

x

x

x

x

x

Word

Stop

5-Byte

x

x

0

1

1

Byte

4-Byte

x

x

1

0

0

6-Byte

x

x

0

1

0

Byte

5-Byte

x

x

0

1

1

x

x

0

1

0

Half

4-Byte

x

x

1

0

0

7-Byte

x

x

0

0

1

Byte

6-Byte

x

x

0

1

0

8-Byte

x

x

0

0

0

Byte

7-Byte

x

x

0

0

1

x

x

0

0

0

Half

6-Byte

x

x

0

1

0

x

x

0

0

0

Word

4-Byte

x

x

1

0

0

x

x

0

0

0

Double

Stop