Freescale Semiconductor MPC8260 User Manual

Page 154

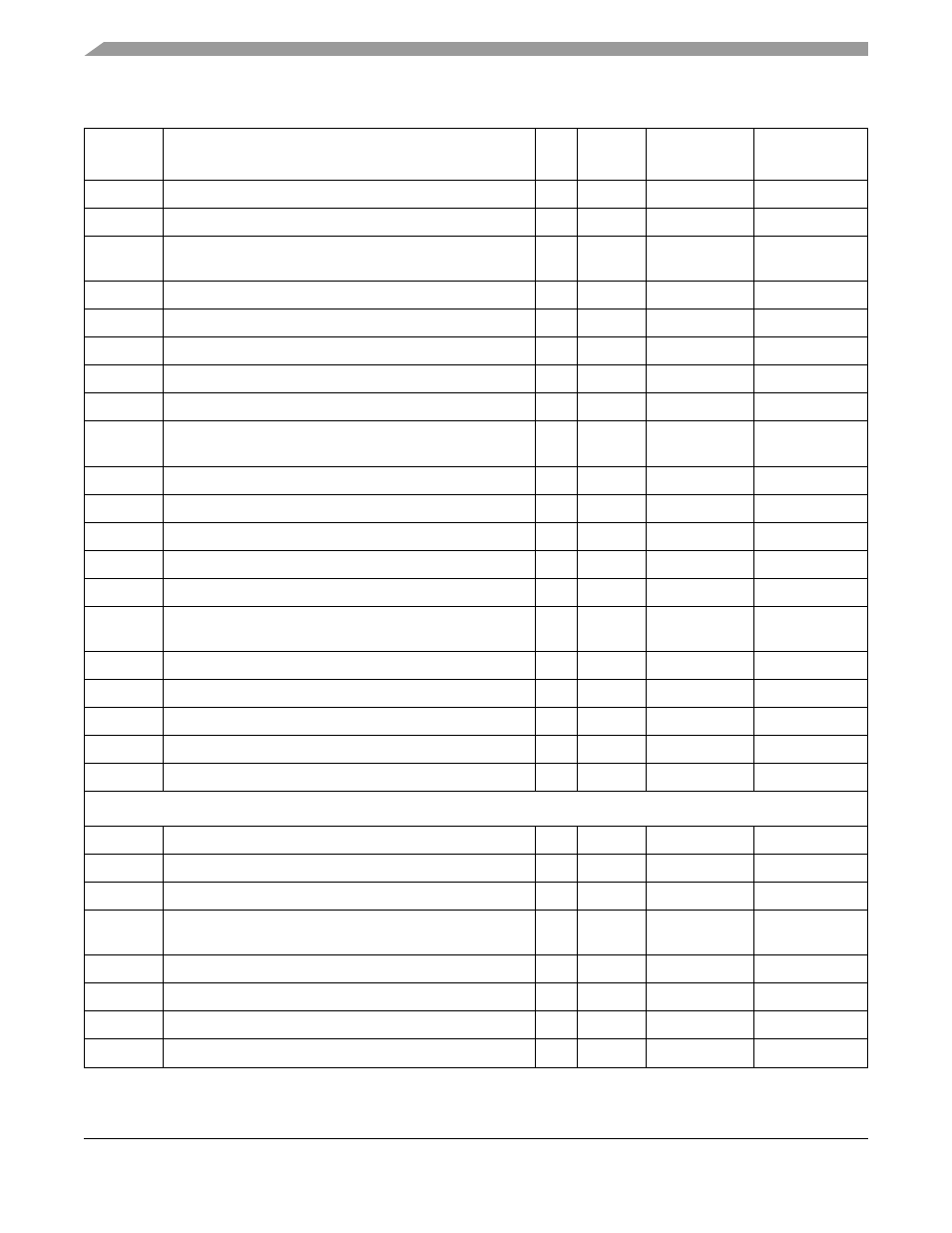

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

3-8

Freescale Semiconductor

0x10D0C

Port A open drain register (PODRA)

R/W

32 bits

0x0000_0000

0x10D10

Port A data register (PDATA)

R/W

32 bits

0x0000_0000

0x10D14–

0x10D1F

Reserved

—

12 bytes

—

—

0x10D20

Port B data direction register (PDIRB)

R/W

32 bits

0x0000_0000

0x10D24

Port B pin assignment register (PPARB)

R/W

32 bits

0x0000_0000

0x10D28

Port B special option register (PSORB)

R/W

32 bits

0x0000_0000

0x10D2C

Port B open drain register (PODRB)

R/W

32 bits

0x0000_0000

0x10D30

Port B data register (PDATB)

R/W

32 bits

0x0000_0000

0x10D34–

0x10D3F

Reserved

—

12 bytes

—

—

0x10D40

Port C data direction register (PDIRC)

R/W

32 bits

0x0000_0000

0x10D44

Port C pin assignment register (PPARC)

R/W

32 bits

0x0000_0000

0x10D48

Port C special option register (PSORC)

R/W

32 bits

0x0000_0000

0x10D4C

Port C open drain register (PODRC)

R/W

32 bits

0x0000_0000

0x10D50

Port C data register (PDATC)

R/W

32 bits

0x0000_0000

0x10D54–

0x10D5F

Reserved

—

12 bytes

—

—

0x10D60

Port D data direction register (PDIRD)

R/W

32 bits

0x0000_0000

0x10D64

Port D pin assignment register (PPARD)

R/W

32 bits

0x0000_0000

0x10D68

Port D special option register (PSORD)

R/W

32 bits

0x0000_0000

0x10D6C

Port D open drain register (PODRD)

R/W

32 bits

0x0000_0000

0x10D70

Port D data register (PDATD)

R/W

32 bits

0x0000_0000

CPM Timers

0x10D80

Timer 1 and timer 2 global configuration register (TGCR1)

R/W

8 bits

0x00

0x10D81

Reserved

—

24 bits

—

—

0x10D84

Timer 3 and timer 4 global configuration register (TGCR2)

R/W

8 bits

0x00

0x10D85–

0x10D8F

Reserved

—

11 bytes

—

—

0x10D90

Timer 1 mode register (TMR1)

R/W

16 bits

0x0000

0x10D92

Timer 2 mode register (TMR2)

R/W

16 bits

0x0000

0x10D94

Timer 1 reference register (TRR1)

R/W

16 bits

0x0000

0x10D96

Timer 2 reference register (TRR2)

R/W

16 bits

0x0000

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page