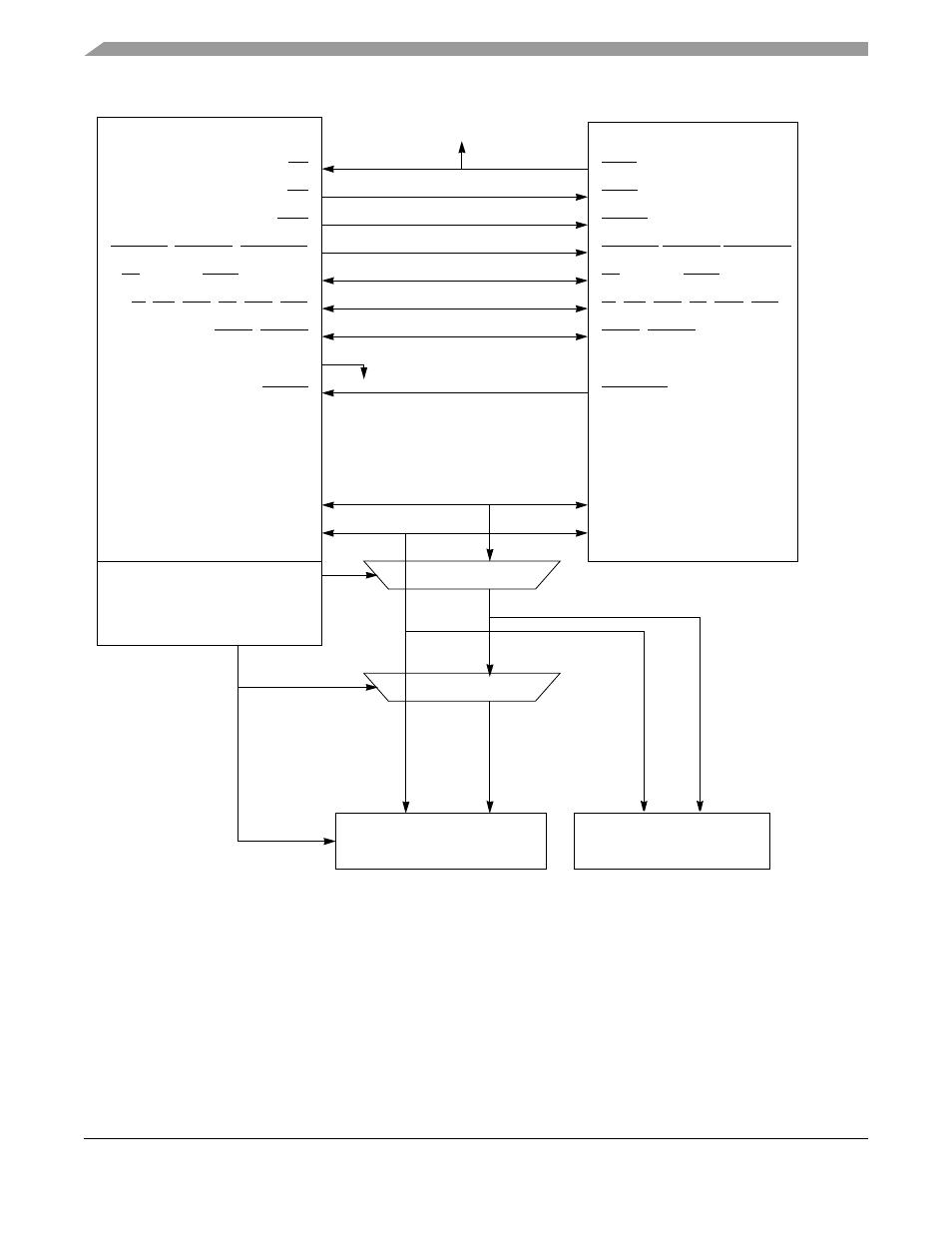

Figure 12-1. l2 cache in copy-back mode, 2 write-through mode, Write-through mode -2 – Freescale Semiconductor MPC8260 User Manual

Page 526: L2 cache in copy-back mode -2

Secondary (L2) Cache Support

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

12-2

Freescale Semiconductor

Figure 12-1. L2 Cache in Copy-Back Mode

12.1.2

Write-Through Mode

In write-through mode, cacheable write operations are performed to both the L2 cache and to main

memory. Since every cacheable write operation goes to the L2 cache and to main memory, write operation

latency is the same as an ordinary memory write transaction. In write-through mode, cacheable read

operations that hit in the L2 cache are serviced from the L2 cache without requiring a memory transaction

and its associated latency. Thus, reads are serviced just as they are for copy-back mode. Write-through

BR

DBG

TS, TT[0–4], TBST, TSIZ[1–3]

A[0–31]

CI, WT, GBL, TA, DBB, TEA

CPU_BR, CPU_BG, CPU_DBG

D[0–63]

PowerQUICC II

L2BR

L2DBG

TS, TT[0–4], TBST, TSIZ[0–2]]

CI, WT, GBL, TA, DBB, TEA

AACK, ARTRY

AACK, ARTRY

CPU_BR,CPU_BG,CPU_DBG

L2_CLAIM

L2_HIT

A[0–31]

D[0–63]

Memory Controller

SDRAM Main Memory

Latch

MUX

I/O Devices

MPC2605

BG

L2BG

TSIZ[0]

(pull down)

(pull up)