Freescale Semiconductor MPC8260 User Manual

Page 558

Communications Processor Module Overview

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

14-10

Freescale Semiconductor

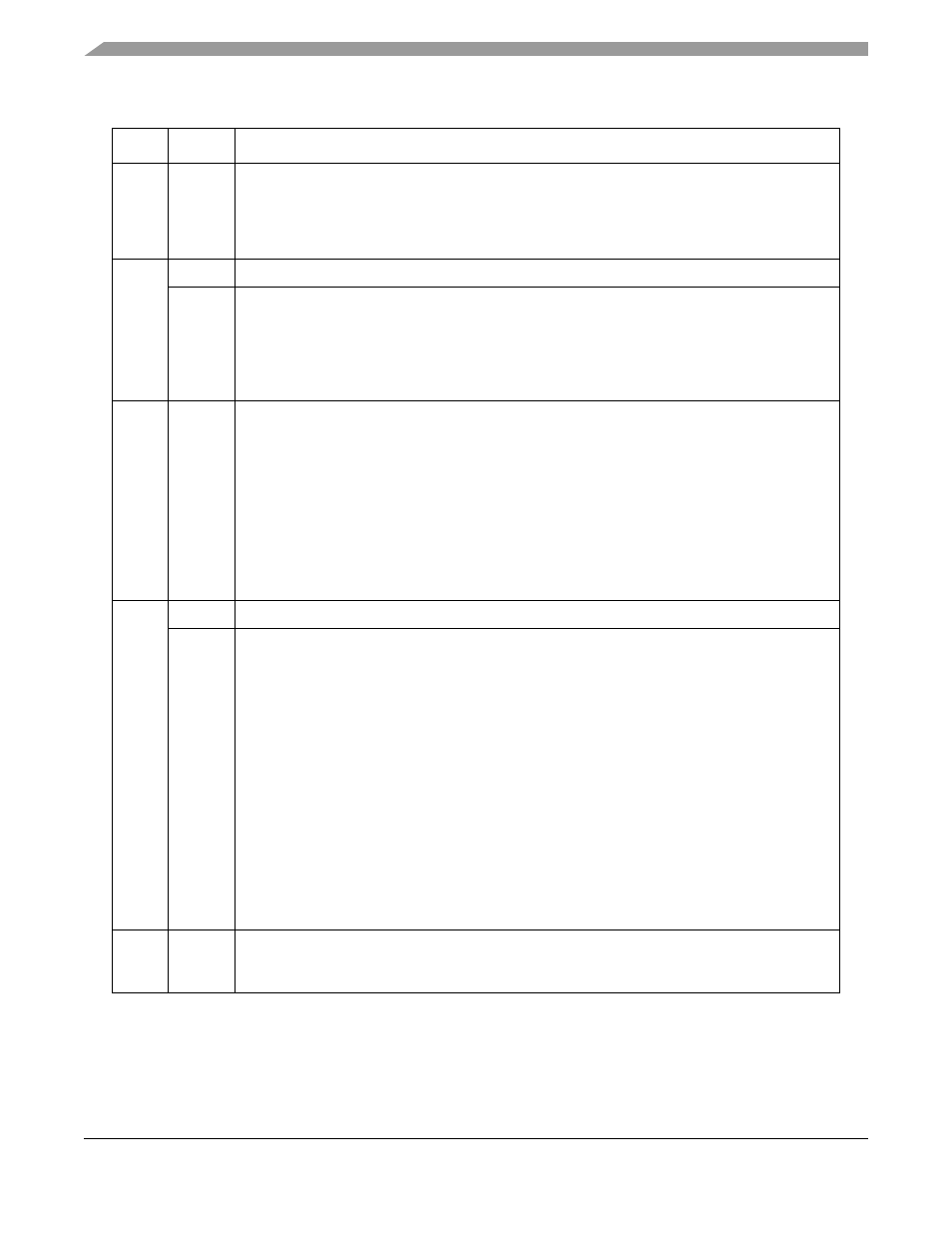

12

EIE

External interrupt enable. When EIE is set, DREQ1 acts as an external interrupt to the CP.

Configure as instructed in the download process of a Freescale-supplied RAM microcode

package.

0 DREQ1 cannot interrupt the CP.

1 DREQ1 will interrupt the CP.

13

—

.29

µm (HiP3) devices: Reserved

SCD

.25

µm (HiP4) devices: Scheduler configuration. Configure as instructed in the download process

of a Freescale-supplied RAM microcode package.

0 Normal operation

1 Alternate configuration of the scheduler, according to bit 19 (in the ERAM field):

If RCCR[19] = 0, the jump table starts at dual-port RAM address 0x0000.

If RCCR[19] = 1, the jump table starts at dual-port RAM address 0x4000.

16–18

ERAM

.29

µm (HiP3) devices: Enable RAM microcode. Configure as instructed in the download process

of a Freescale-supplied RAM microcode package. (For .25

µm (HiP4) devices RCCR[ERAM] =

16–19. See the following row for settings.)

000 Disable microcode program execution from the dual-port RAM.

001 Microcode uses the first 2 Kbytes of the dual-port RAM.

010 Microcode uses the first 4 Kbytes of the dual-port RAM.

011 Microcode uses the first 6 Kbytes of the dual-port RAM.

100 Microcode uses the first 8 Kbytes of the dual-port RAM.

101 Microcode uses the first 10 Kbytes of the dual-port RAM.

110 Microcode uses the first 12 Kbytes of the dual-port RAM.

111 Reserved

19

—

.29

µm (HiP3) devices: Reserved

ERAM

.25

µm (HiP4) devices: ERAM[16-19] .Enable RAM microcode. Configure as instructed in the

download process of a Freescale-supplied RAM microcode package.

0000 Disable microcode program execution from the dual-port RAM. (That is, microcode

execution starts at ROM address 0x0000 after reset.)

In the following configurations, RAM microcode execution starts at address 0x0000 after reset:

0010 Microcode uses the first 2 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

0100 Microcode uses the first 4 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

0110 Microcode uses the first 6 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

1000 Microcode uses the first 8 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

1010 Microcode uses the first 10 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

1100 Microcode uses the first 12 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

In the following configurations, microcode execution starts at RAM address 0x4000 after reset:

0011 Microcode uses 2 Kbytes starting from dual-port RAM address 0x4000.

0101 Microcode uses 4 Kbytes starting from dual-port RAM address 0x4000.

0111 Microcode uses 6 Kbytes starting from dual-port RAM address 0x4000.

1001 Microcode uses 8 Kbytes starting from dual-port RAM address 0x4000.

Note: All other configurations not listed are reserved.

20, 21,

22, 23

EDM

x

Edge detect mode. DREQ

x

asserts as follows:

0 Low-to-high change

1 High-to-low change

Table 14-3. RISC Controller Configuration Register Field Descriptions (continued)

Bits

Name Description