Freescale Semiconductor MPC8260 User Manual

Page 1147

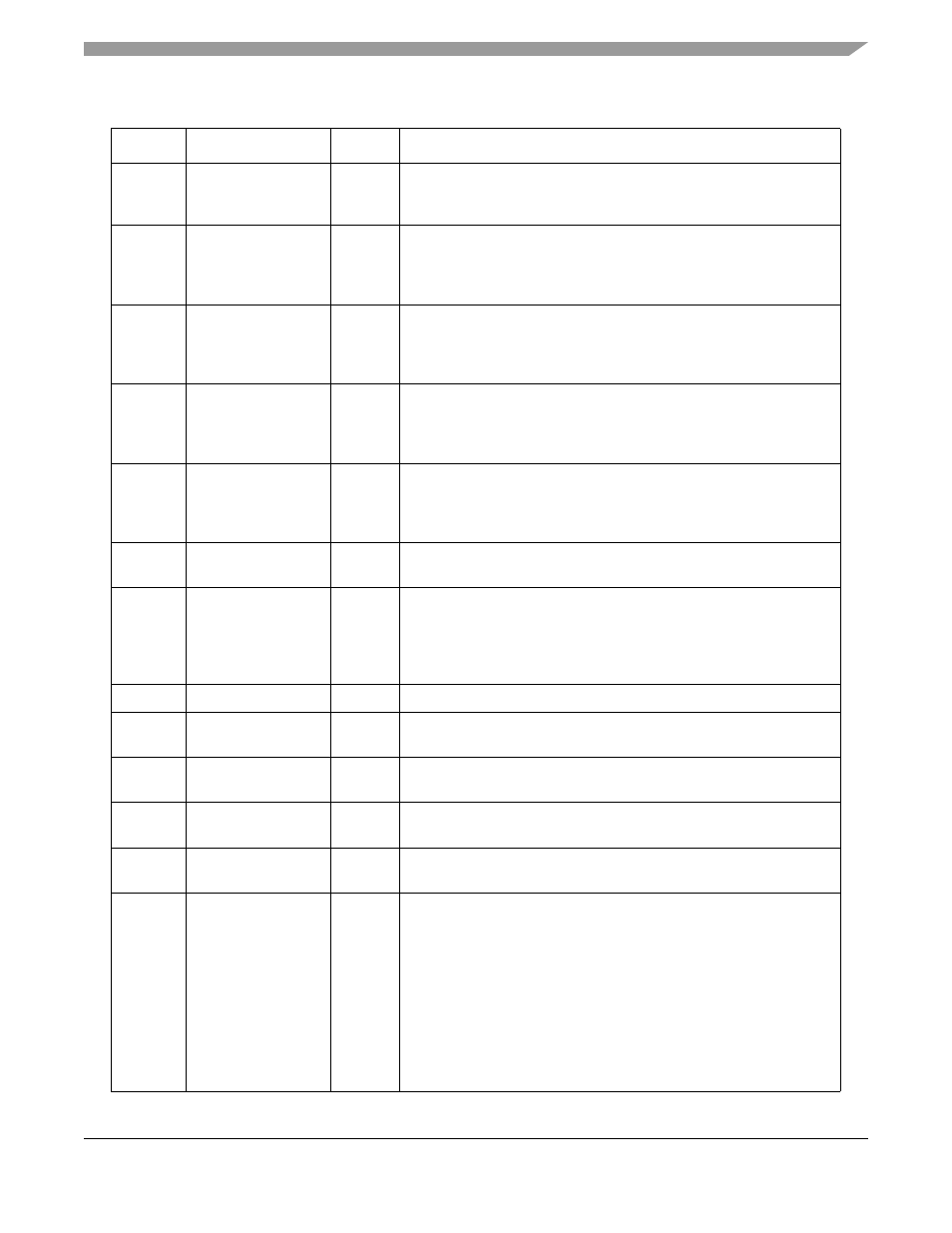

Inverse Multiplexing for ATM (IMA)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

33-45

0x07

DFC

Byte

Number of frames to discard on a this link until it is caught up with the

other links in this group (long propagation delay). Microcode-managed

parameter.

0x08

DCBSP

Hword

IMA link delay compensation buffer start pointer. This parameter forms

bits 12-27 of the pointer; bits 0-11 are from IMAEXTBASE, and bits

28-31 are zero. Refer to

Section 33.4.6.2, “Delay Compensation

for more details.

0x0A

DCBEP

Hword

IMA link delay compensation buffer end pointer. This parameter forms

bits 12-27 of the pointer; bits 0-11 are from IMAEXTBASE, and bits

28-31 are zero. Refer to

Section 33.4.6.2, “Delay Compensation

for more details.

0x0C

DCBFP

Hword

IMA link delay compensation buffer fill pointer. Microcode-managed

parameter. This parameter forms bits 12-27 of the pointer; bits 0-11 are

from IMAEXTBASE, and bits 28-31 are zero.

Initialize to DCBSP at link startup.

0x0E

DCBRP

Hword

IMA link delay compensation buffer read pointer. Only used during

group delay synchronization and link addition. Microcode-managed

parameter. This parameter forms bits 12-27 of the pointer; bits 0-11 are

from IMAEXTBASE, and bits 28-31 are zero.

0x10

RICPCH

Hword

Receive ICP channel number. ATM receive channel number to which

received ICP cells are sent.

0x12

IRINTMSK

Byte

IMA receive interrupt mask. Has the same format as the IMA interrupt

queue entry.; however, only receive-related bits are relevant. Setting a

bit enables the associated interrupt; clearing a bit masks it.

For group-related events, only the mask register for the TRL is

referenced.

0x13

LICPOS

Byte

Link ICP offset. Program to the ICP offset validated for this link.

0x14

IRSEC

Word

IMA receive stuff event counter. Increments each time a stuff event is

received on this ink. Initialize to zero at link startup.

0x18

ANOMALY_CTR

Byte

Anomaly counter. Microcode-managed parameter. Initialize to zero at

link startup.

0x19

ALPHABETA_CTR

Byte

Alpha/beta counter. Microcode-managed parameter. Initialize to zero at

link startup.

0x1A

GAMMA_CTR

Byte

Gamma counter. Microcode-managed parameter. Initialize to zero at

link startup.

0x1C

DEFECT_CTR

Word

Defect counter. This counter is active while the link is in the

Loss-of-IMA-Frame (LIF) state and is used to ensure IFSD interrupts

are generated for every GAMMA+2 frames. Software can use the

period interrupt issued by this counter in order to determine if the link

is taking too long to synchronize. The DEFECT_CTR is active before

IFSM reaches SYNC. It starts counting from the first cell received and

will count from 0 to (GAMMA+2) x M. When it reaches (GAMMA+2) x M

an IFSD interrupt is generated and the counter is reset. Upon reception

of the next cell it starts to count again and subsequent interrupts are

generated. Microcode managed parameter. Initialize to zero at link

startup.

Table 33-19. IMA Link Receive Table Entry

1

(continued)

Offset Name

Width

Description