Freescale Semiconductor MPC8260 User Manual

Page 150

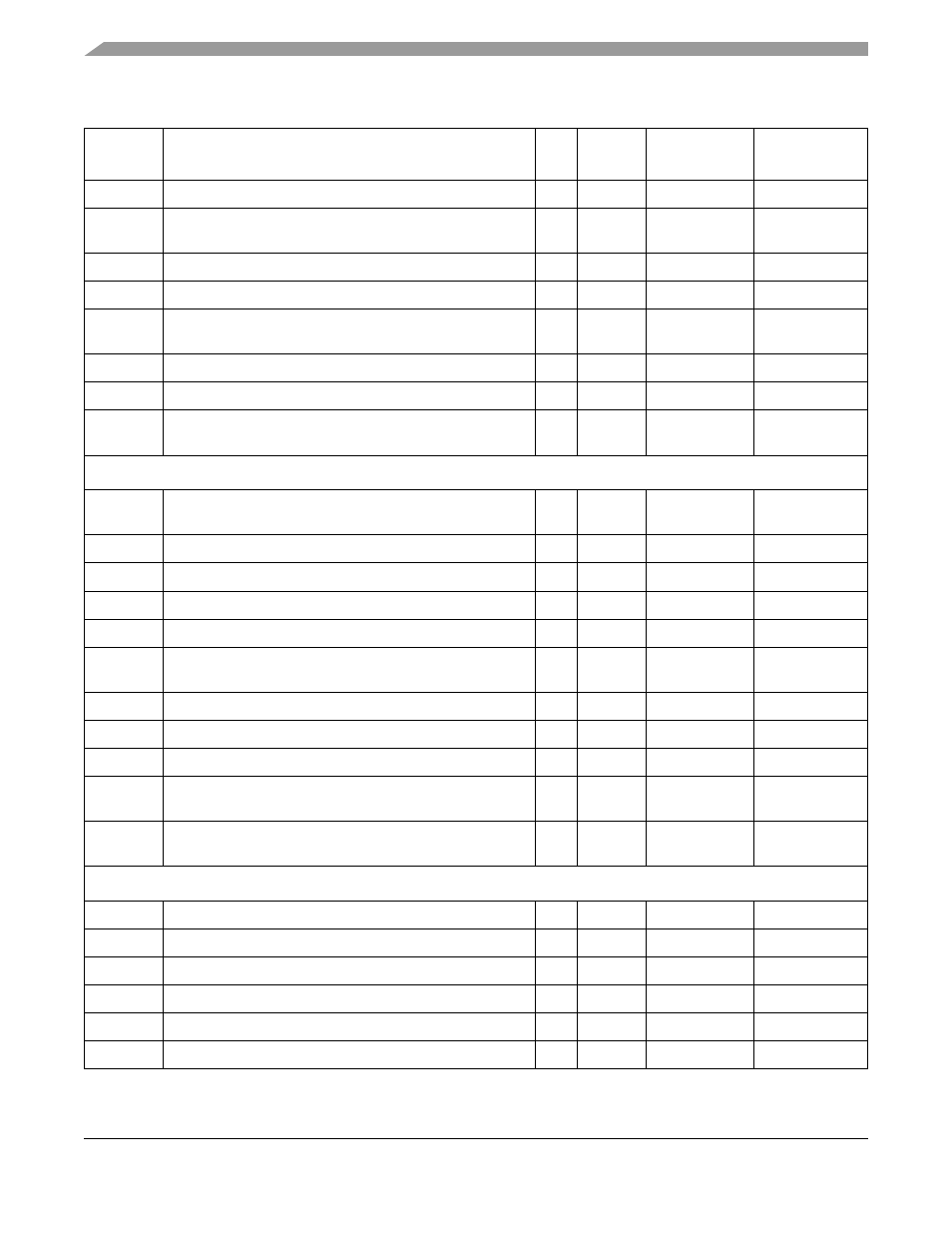

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

3-4

Freescale Semiconductor

0x101A5

Reserved

—

24 bits

—

—

0x101A8

Internal memory map register (IMMR)

R/W

32 bits

reset

configuration

0x101AC

PCI base register 0 (PCIBR0)

2

R/W

bits

0x0000_0000

0x101B0

PCI base register 1 (PCIBR1)

2

R/W

32 bits

0x0000_0000

0x101B4–

0x101C3

Reserved

—

16 bytes

—

—

0x101C4

PCI mask register 0 (PCIMSK0)

2

R/W

32 bits

0x0000_0000

0x101C8

PCI mask register 1 (PCIMSK1)

2

R/W

32 bits

0x0000_0000

0x101CC–

0x101FF

Reserved

—

52 bytes

—

—

System Integration Timers

0x10200–

0x10 21F

Reserved

—

32 bytes

—

—

0x10220

Time counter status and control register (TMCNTSC)

R/W

16 bits

0x0000

0x10224

Time counter register (TMCNT)

R/W

32 bits

0x0000_0000

0x10228

Reserved

—

32 bits

—

—

0x1022C

Time counter alarm register (TMCNTAL)

R/W

32 bits

0x0000_0000

0x10230–

0x1023F

Reserved

—

16 bytes

—

—

0x10240

Periodic interrupt status and control register (PISCR)

R/W

16 bits

0x0000

0x10244

Periodic interrupt count register (PITC)

R/W

32 bits

0x0000_0000

0x10248

Periodic interrupt timer register (PITR)

R

32 bits

0x0000_0000

0x1024C–

0x102A8

Reserved

—

92 bytes

—

—

0x102AA–

0x1042F

Reserved

—

372

bytes

—

—

PCI

2

0x10430

Outbound interrupt status register (OMISR)

2

R/W

32 bits

0x0000_0000

0x10434

Outbound interrupt mask register (OMIMR)

2

R/W

32 bits

0x0000_0000

0x10440

Inbound FIFO queue port register (IFQPR)

2

R/W

32 bits

0x0000_0000

0x10444

Outbound FIFO queue port register (OFQPR)

2

R/W

32 bits

0x0000_0000

0x10450

Inbound message register 0 (IMR0)

2

R/W

32 bits

undefined

0x10454

Inbound message register 1 (IMR1)

2

R/W

32 bits

undefined

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page