3 programming dts and sts, Table 19-7. valid memory-to-memory sts/dts values, Programming dts and sts -22 – Freescale Semiconductor MPC8260 User Manual

Page 666: Valid memory-to-memory sts/dts values -22, Table 19-7

SDMA Channels and IDMA Emulation

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

19-22

Freescale Semiconductor

19.8.2.3

Programming DTS and STS

The options for setting STS and DTS depend on (DCM[DMA_WRAP]) and are described in the following

tables for memory/memory and memory/peripheral transfers.

describes valid STS/DTS values for memory-to-memory operations.

00

0

Memory

(STS = SS_MAX

or less)

Memory

(DTS =

SS_MAX)

Read from memory: Filling internal buffer in one or more DMA

transfers.

On the bus: singles or bursts, depends on STS

Write to memory: in one DMA transfer, internal buffer empties.

On the bus: one burst or more, depends on DTS

01

1

Memory to

peripheral

(DTS = port size or

32)

—

Read transaction from memory while asserting DACK to

peripheral. Peripheral samples the data read from memory.

On the bus: singles or bursts, depends on DTS

10

1

—

Peripheral to

memory

(STS = port size

or 32)

Write transaction to memory while asserting DACK to peripheral.

Peripheral provides the data that is written to the memory.

On the bus: singles or bursts, depends on STS

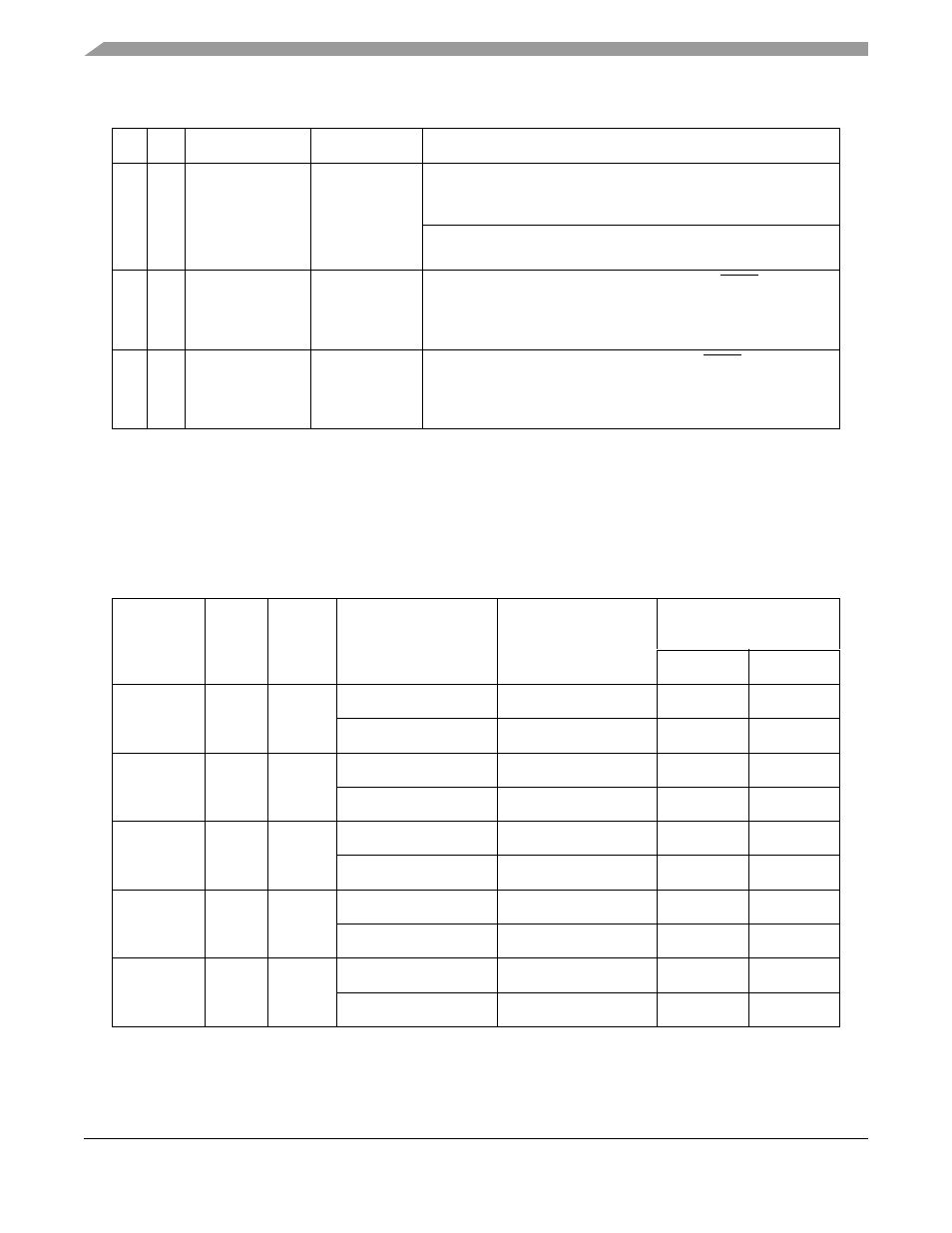

Table 19-7. Valid Memory-to-Memory STS/DTS Values

DMA_WRAP

Internal

Buffer

Size

SS_MAX

STS (in Bytes)

DTS (in Bytes)

Number of Transfers to Fill

Internal Buffer

STS Size

DTS Size

000

64

1 * 32

1 * 32

32

1

1

32

1 * 32

1

1

001

128

3 * 32

3 * 32

3 * 32, 32

1

1, 3

3 * 32, 32

3 * 32

1, 3

1

010

256

7 * 32

7 * 32

7 * 32, 32

1

1, 7

7 * 32, 32

7 * 32

1, 7

1

011

512

15 * 32

15 * 32

15 * 32, 3 * 32, 5 * 32, 32

1

1, 5, 3, 15

15 * 32, 3 * 32, 5 * 32, 32

15 * 32

1, 5, 3, 15

1

100

1024

31 * 32

31 * 32

31 * 32, 32

1

1, 31

31 * 32, 32

31 * 32

1, 31

1

Table 19-6. IDMA Channel Data Transfer Operation (continued)

S/D

FB

Read From

Write To

Description (Steady-State Operation)