2 pci bridge configuration registers, Pci bridge configuration registers -45, Pci bridge pci configuration registers -45 – Freescale Semiconductor MPC8260 User Manual

Page 351: Pci bridge configuration registers

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-45

9.11.2

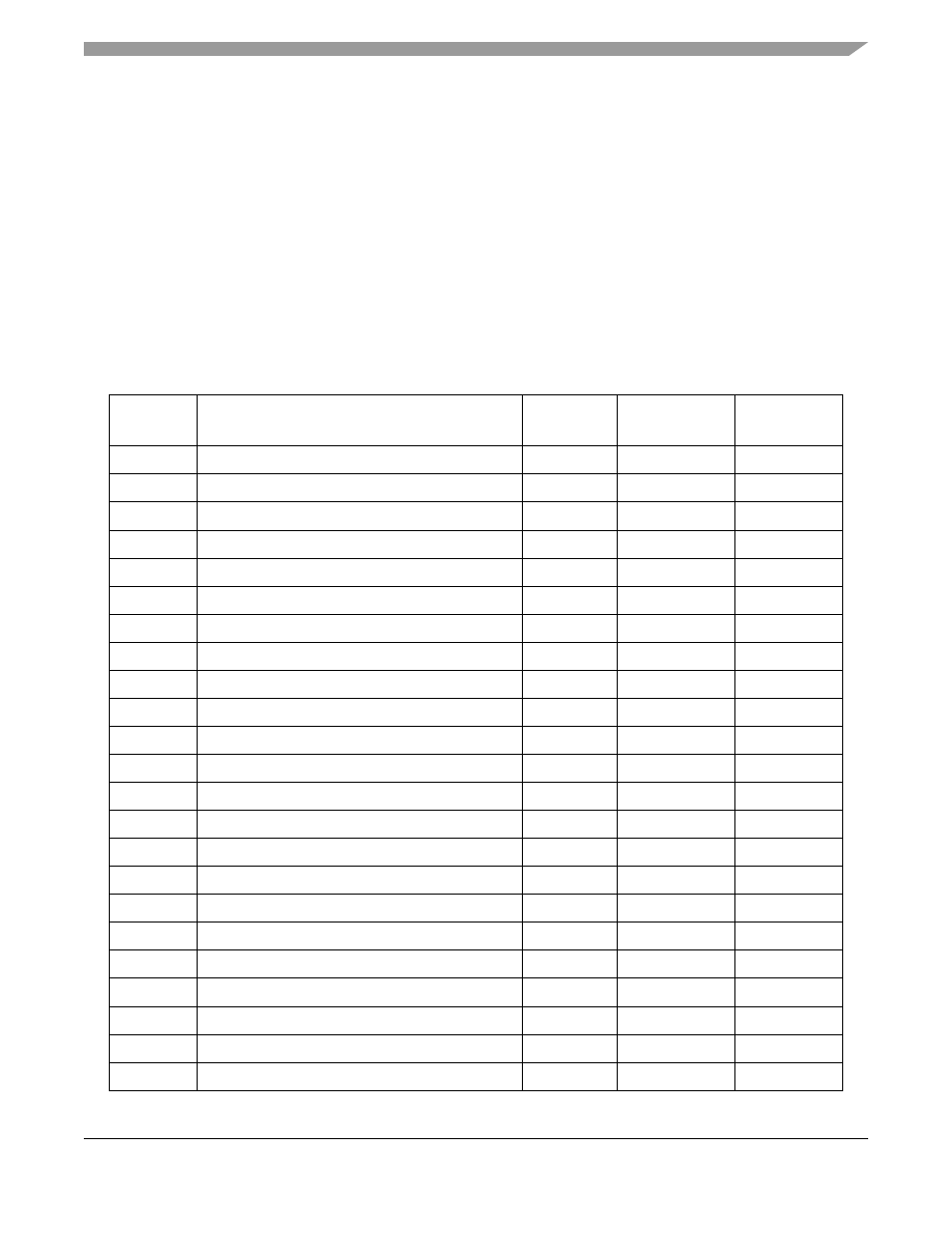

PCI Bridge Configuration Registers

The PCI Local Bus Specification defines the configuration registers from 0x00 through 0x3F. Additionally,

the PCI bridge specifies these additional registers: the PCI function register (at offset 0x44), the PCI arbiter

control register (at offset 0x46), and the PCI Hot Swap register block (at offset 0x48).

and

shows the PCI configuration registers provided by the PCI bridge for the PCI bus.

Note the following sections that apply to all PCI configuration registers (they appear immediately after the

descriptions of individual registers):

•

Section 9.11.2.26, “PCI Configuration Register Access from the Core,” on page 9-62

•

Section 9.11.2.27, “PCI Configuration Register Access in Big-Endian Mode,” on page 9-62

•

Section 9.11.2.28, “Initializing the PCI Configuration Registers,” on page 9-64

Table 9-19. PCI Bridge PCI Configuration Registers

Address

(offset)

Register

Access

Reset

Section/Page

00

Vendor ID

R

0x1057

02

Device ID

R

0x18C0

04

PCI command

R/W

Mode-dependent

06

PCI status

Read/bit-reset

0x00B0

08

Revision ID

R

Rev-dependent

09

Standard programming interface

R

Mode-dependent

0A

Subclass code

R

0x00

0B

Class code

R

Mode-dependent

0C

Cache line size

R/W

0x00

0D

Latency timer

R/W

0x00

0E

Header type

R

0x00

0F

BIST control

R

0x00

10

PIMMR base address register

R/W

0x

nnnn

_0000

14

GPL base address register 0

R/W

0x0000_0000

18

GPL base address register 1

R/W

0x0000_0000

1C

Reserved

—

—

—

2C

Sub system vendor ID

R/W

0x0000

2E

Sub system device ID

R/W

0x0000

30

Reserved

—

—

—

34

Capabilities pointer

R

0x48

35

Reserved

—

—

—

3C

Interrupt line

R/W

0x00

3D

Interrupt pin

R

0x01