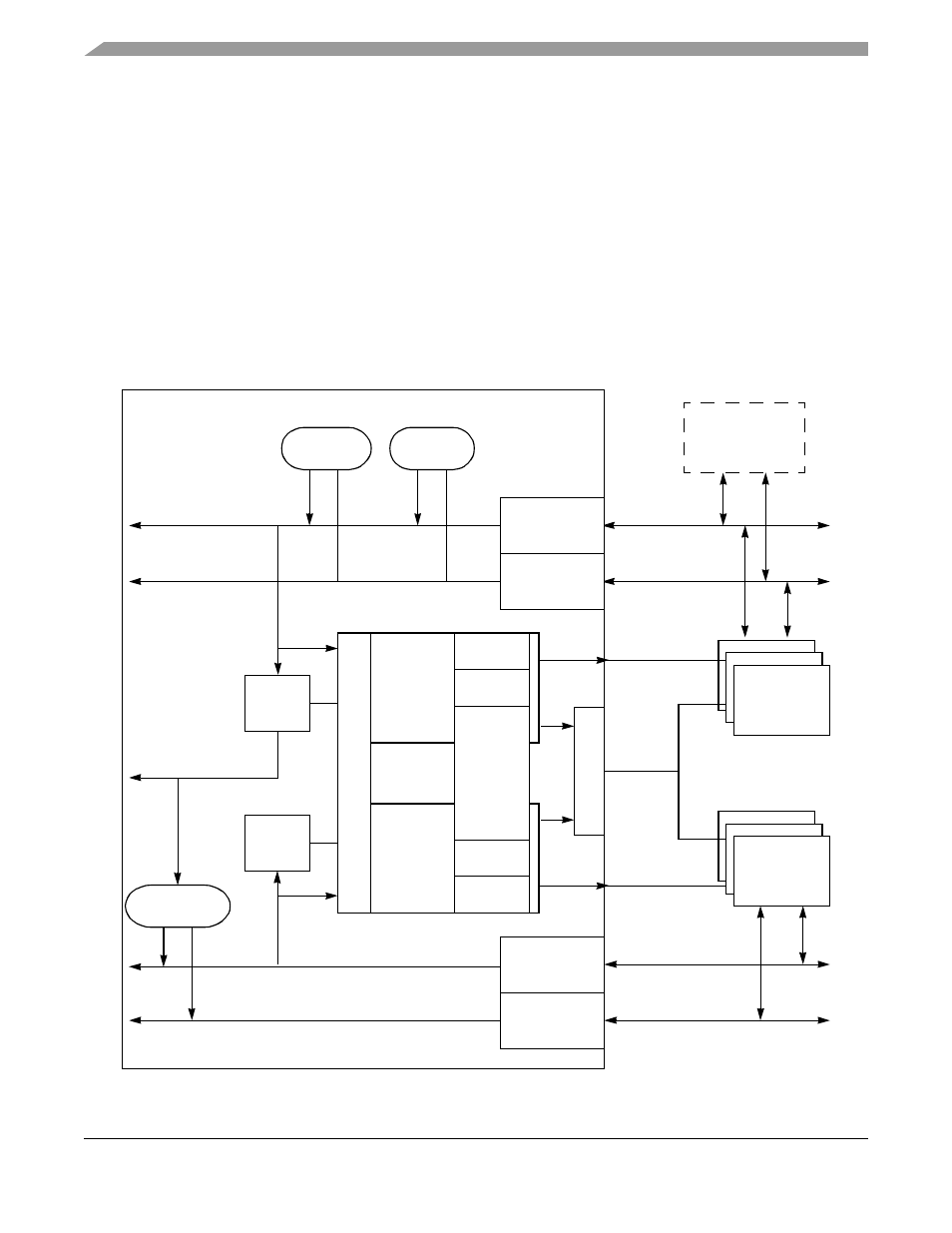

Figure 11-1. dual-bus architecture, Dual-bus architecture -2 – Freescale Semiconductor MPC8260 User Manual

Page 420

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

11-2

Freescale Semiconductor

•

18-bit address and 32-bit local data bus memory controller. The local bus memory controller

supports the following:

— 8-, 16-, and 32-bit port sizes

— Parity checking and generation

— Ability to work in parallel with the 60x bus memory controller

•

Flexible chip-select assignment—The 60x bus and local bus share twelve chip-select lines

(controlled by a memory controller bank). The user can allocate the twelve banks as needed

between the 60x bus and the local bus.

•

Flexible UPM assignment—The user can assign any of the three UPMs to the 60x bus or the Local

bus

shows the dual-bus architecture.

Figure 11-1. Dual-Bus Architecture

PowerQUICC II

A[0–31]

D[0–63]

LA[14–31]

LD[0–31]

External

Master

60x

Local

60x Memory

Control Signals

CS[0–11]

Local Memory

Control Signals

60x Address

Bus Interface

Local Address

Bus Interface

Local Data

Bus Interface

60x Address [0–31]

Local Address [0–31]

60x Data[0–63]

Local Data [0–63]

GPCM

SDRAM

Local

Memory

Controller

SDRAM

GPCM

60x

Memory

Controller

3 UPM

Arrays

Add

res

s De

coder

s

Local

60x-to-Local

Core

CPM/Local

2Æ

1

60x

Transactions

60x Data

Bus Interface

CPM/PCI

Master

Slave

Slave

Memory

Devices

Memory

Devices