2 channel-specific transparent parameters, Channel-specific transparent parameters -11 – Freescale Semiconductor MPC8260 User Manual

Page 859

Multi-Channel Controllers (MCCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

28-11

28.3.2

Channel-Specific Transparent Parameters

describes channel-specific parameters for transparent operation.

6

DTB

Data bus indicator.

The transfers to data buffers are handled by the:

0 60x bus SDMA

1 Local bus SDMA

7

BDB

BD and interrupt circular tables bus indicator.

The transfers to/from BD and interrupt circular tables are handled by the:

0 60x bus SDMA

1 Local bus SDMA

Note: The following restrictions result from the fact that there is a common bus selection bit for BDs

and interrupt circular tables:

• The RxBDs of all the channels that use a particular interrupt table must reside on the same bus

(60x or local).

• All TxBDs must reside on the same bus (60x or local).

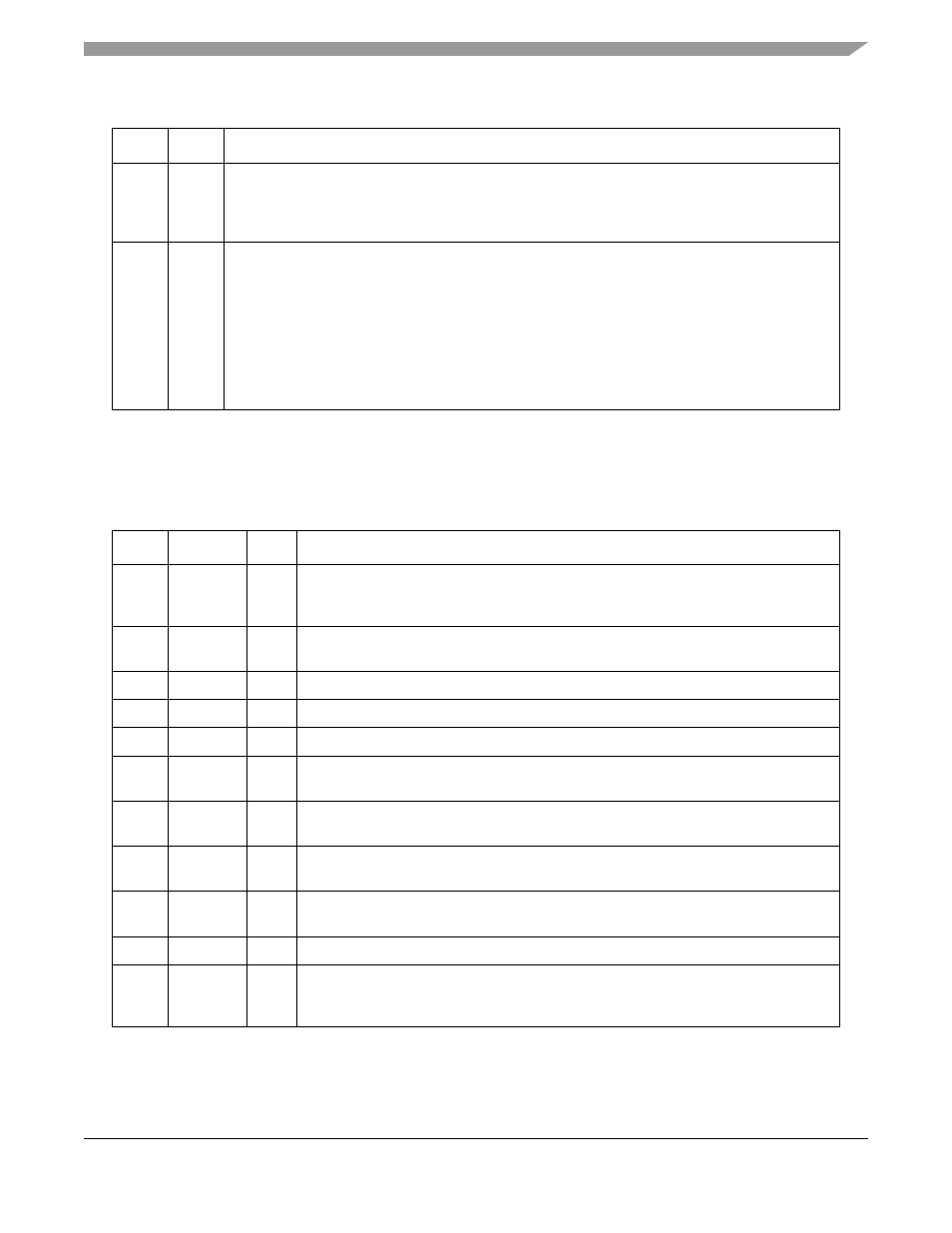

Table 28-6. Channel-Specific Parameters for Transparent Operation

Offset

1

Name

Width

Description

0x00

TSTATE

Word

Tx internal state. To start a transmitter channel the user must write to TSTATE

0xHH80_0000. HH is the TSTATE high byte described in

Transmitter State (TSTATE)—HDLC Mode

.”

0x04

ZISTATE

Word

Zero-insertion machine state.(User-initialized to 0x10000207 for regular channel, and

0x30000207 for inverted channel)

0x08

ZIDATA0

Word

Zero-insertion high word data buffer (User-initialized to 0xFFFFFFFF)

0x0C

ZIDATA1

Word

Zero-insertion low word data buffer (User-initialized to 0xFFFFFFFF)

0x10

TBDFlags

Hword TxDB flags, used by the CP (read-only for the user)

0x12

TBDCNT

Hword Tx internal byte count. Number of remaining bytes in buffer, used by the CP (read-only

for the user)

0x14

TBDPTR

Word

Tx internal data pointer. Points to current absolute data address of channel, used by the

CP (read-only for the user)

0x18

INTMSK

Hword Channel’s interrupt mask flag. See

Section 28.3.3.1.1, “Interrupt Circular Table Entry

and Interrupt Mask (INTMSK)—AAL1 CES

.”

0x1A

CHAMR

Hword Channel mode register. See

Section 28.3.2.3, “Channel Mode Register

.”

0x1C

—

Word

Reserved

0x20

RSTATE

Word

Rx internal state. To start a receiver channel the user must write to RSTATE

0xHH80_0000. HH is the RSTATE high byte described in

Receiver State (RSTATE)—HDLC Mode

Table 28-5. RSTATE High-Byte Field Descriptions (continued)

Bits

Name

Description