Freescale Semiconductor MPC8260 User Manual

Page 957

ATM Controller and AAL0, AAL1, and AAL5

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

30-37

0x44

UDC_TMP_BASE

Hword UDC mode only. Points to a total of 64 bytes reserved dual-port RAM area

used by the CP. Should be 64-byte aligned. User-defined offset from

dual-port RAM base. (Recommended address space: 0x3000–0x4000 or

0xB000–0xC000)

0x46

INT_RCT_BASE

Hword Internal receive connection table base. User-defined offset from dual-port

RAM base.

0x48

INT_TCT_BASE

Hword Internal transmit connection table base. User-defined offset from

dual-port RAM base.

0x4A

INT_TCTE_BASE

Hword Internal transmit connection table extension base. User-defined offset

from dual-port RAM base.

0x4C

—

Word

Reserved, should be cleared.

0x50

EXT_RCT_BASE

Word

External receive connection table base. User-defined.

0x54

EXT_TCT_BASE

Word

External transmit connection table base. User-defined.

0x58

EXT_TCTE_BASE

Word

External transmit connection table extension base. User-defined.

0x5C

UEAD_OFFSET

Hword User-defined cells mode only. Offset to the user-defined extended

address (UEAD) in the UDC extra header. Must be an even address. See

Section 30.10.1.1, “Determining UEAD_OFFSET (UEAD Mode Only)

If RCT[BO] = 01, UEAD_OFFSET should be in little-endian format. For

example, if the UEAD entry is the first half word of the extra header in

external memory, UEAD_OFFSET should be programmed to 2 (second

half word entry in dual-port RAM).

0x5E

—

Hword Reserved, should be cleared.

0x60

PMT_BASE

Hword Performance monitoring table base. User-defined offset from dual-port

RAM base.

0x62

APCP_BASE

Hword APC parameter table base address. User-defined offset from dual-port

RAM base.

0x64

FBT_BASE

Hword Free buffer pool parameter table base. User-defined offset from dual-port

RAM base.

0x66

INTT_BASE

Hword Interrupt queue parameter table base. User-defined offset from dual-port

RAM base.

0x68

—

—

Reserved, should be cleared.

0x6A

UNI_STATT_BASE

Hword UNI statistics table base. User-defined offset from dual-port RAM base.

Note that this must be set up according to Section 29.10.7, “UNI Statistics

Table>” It is not optional.

0x6C

BD_BASE_EXT

Word

BD table base address extension. BD_BASE_EXT[0–7] holds the 8

most-significant bits of the Rx/Tx BD table base address.

BD_BASE_EXT[8–31] should be zero. User-defined.

0x70

VPT_BASE /

EXT_CAM_BASE

Word

Base address of the address compression VP table/external CAM.

User-defined.

0x74

VCT_BASE

Word

Base address of the address compression VC table. User-defined.

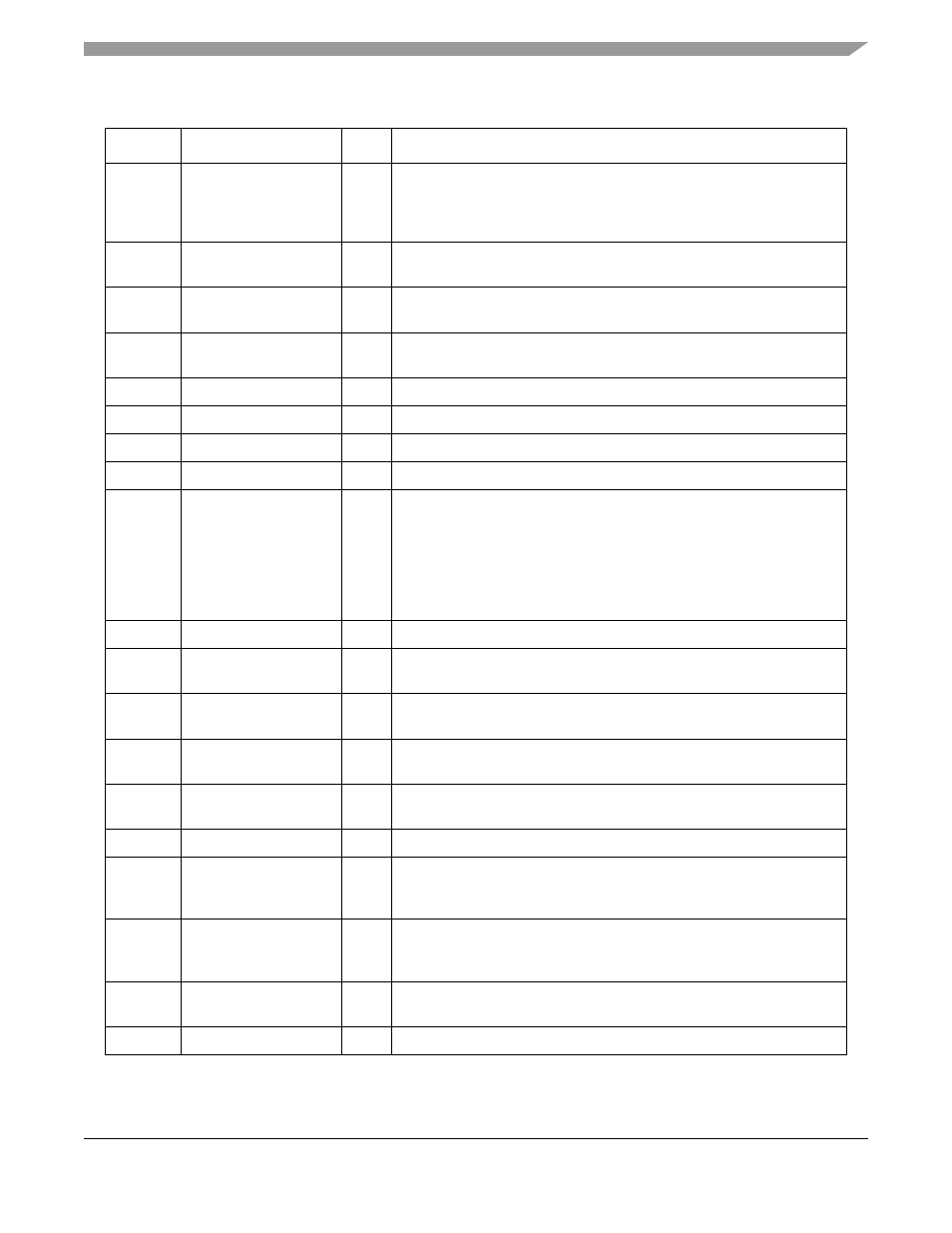

Table 30-11. ATM Parameter RAM Map (continued)

Offset

1

Name

Width

Description