Freescale Semiconductor MPC8260 User Manual

Page 684

Serial Communications Controllers (SCCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

20-6

Freescale Semiconductor

1–2

EDGE

Clock edge. Determines the clock edge the DPLL uses to adjust the receive sample point due to

jitter in the received signal. Ignored in UART protocol or if the 1x clock mode is selected in RDCR.

00 Both the positive and negative edges are used for changing the sample point (default).

01 Positive edge. Only the positive edge of the received signal is used to change the sample point.

10 Negative edge. Only the negative edge of the received signal is used to change the sample

point.

11 No adjustment is made to the sample point.

3

TCI

Transmit clock invert.

0 Normal operation.

1 Before it is used, the internal Tx clock (TCLK) is inverted by the SCC so it can clock data out

one-half clock earlier (on the rising rather than the falling edge). In this case, the SCC offers a

minimum and maximum rising clock edge-to-data specification. Data output by the SCC after the

rising edge of an external Tx clock can be latched by the external receiver one clock cycle later

on the next rising edge of the same Tx clock. The edge on which the SCC outputs the data

depends on the mode of operation:

• In HDLC and Transparent mode, when TCI=0, data is sent on the falling edge; when TCI=1, on

the rising edge.

• In Ethernet mode, when TCI=0, data is sent on the rising edge; when TCI=1, on the falling edge.

Note: Recommended for Ethernet, HDLC, and transparent operation when clock rates exceed 8

MHz to improve data setup time for the external transceiver.

4–5

TSNC

Transmit sense. Determines the amount of time the internal carrier sense signal stays active after

the last transition on RXD, indicating that the line is free. For instance, AppleTalk can use TSNC to

avoid a spurious CS-changed (SCCE[DCC]) interrupt that would otherwise occur during the frame

sync sequence before the opening flags. If RDCR is configured to 1

× clock mode, the delay is the

greater of the two numbers listed. If RDCR is configured to 8

Ч, 16Ч, or 32× mode, the delay is the

smaller number.

00 Infinite. Carrier sense is always active (default).

01 14- or 6.5-bit times as determined by RDCR.

10 4- or 1.5-bit times as determined by RDCR (normally for AppleTalk).

11 3- or 1-bit times as determined by RDCR.

6

RINV

DPLL Rx input invert data. Must be zero in HDLC bus mode or asynchronous UART mode.

0 Do not invert.

1 Invert data before sending it to the DPLL for reception. Used to produce FM1 from FM0 and NRZI

space from NRZI mark or to invert the data stream in regular NRZ mode.

7

TINV

DPLL Tx input invert data. Must be zero in HDLC bus mode.

0 Do not invert.

1 Invert data before sending it to the DPLL for transmission. Used to produce FM1 from FM0 and

NRZI space from NRZI mark and to invert the data stream in regular NRZ mode. In T1

applications, setting TINV and TEND creates a continuously inverted HDLC data stream.

8–10

TPL

Tx preamble length. Determines the length of the preamble configured by the TPP bits.

000 No preamble (default).

001 8 bits (1 byte).

010 16 bits (2 bytes).

011 32 bits (4 bytes).

100 48 bits (6 bytes). Select this setting for Ethernet operation.

101 64 bits (8 bytes).

110 128 bits (16 bytes).

111 Reserved.

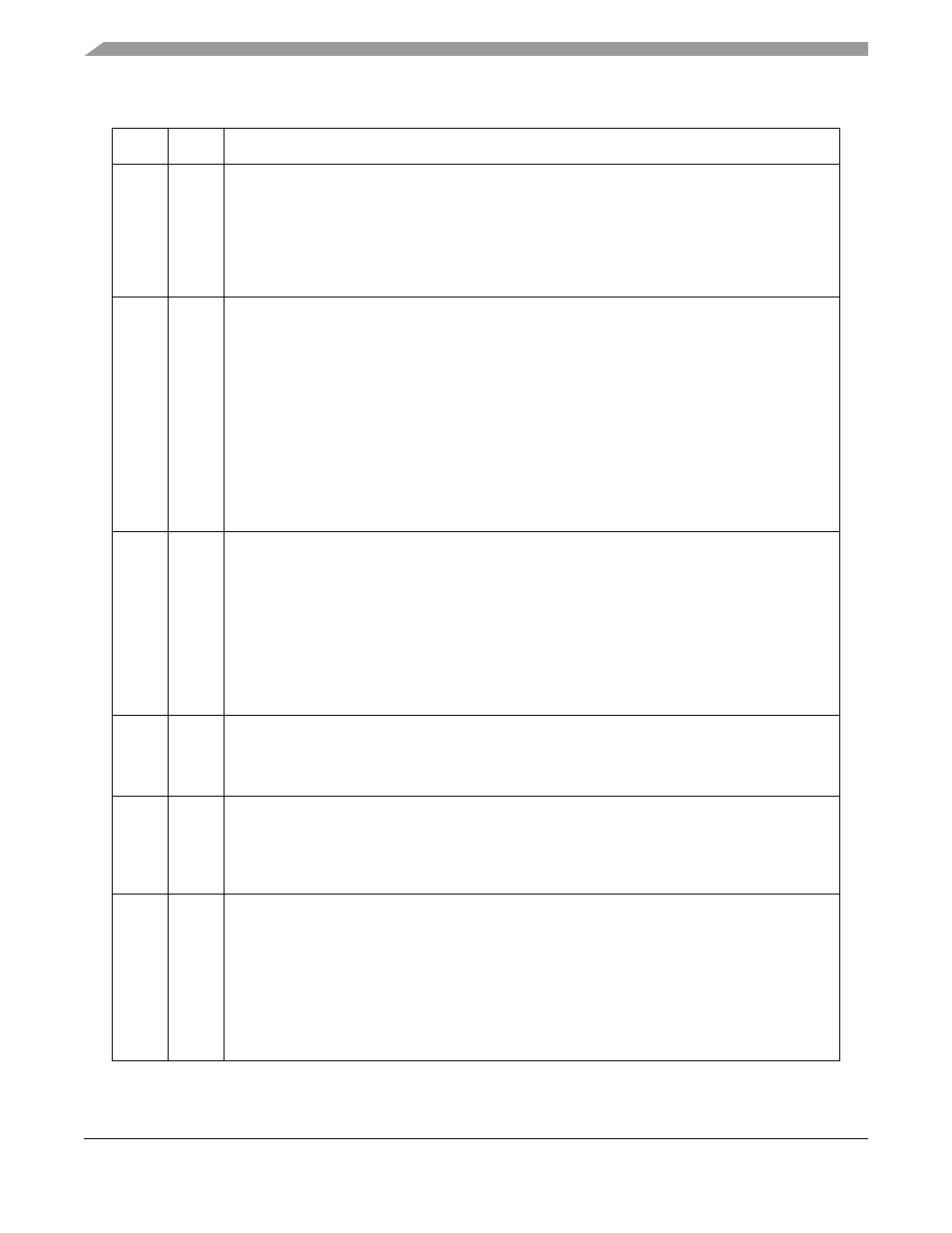

Table 20-2. GSMR_L Field Descriptions (continued)

Bit

Name

Description