Figure 27-11. synchronization with smsynx, Synchronization with smsyn – Freescale Semiconductor MPC8260 User Manual

Page 835

Serial Management Controllers (SMCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

27-23

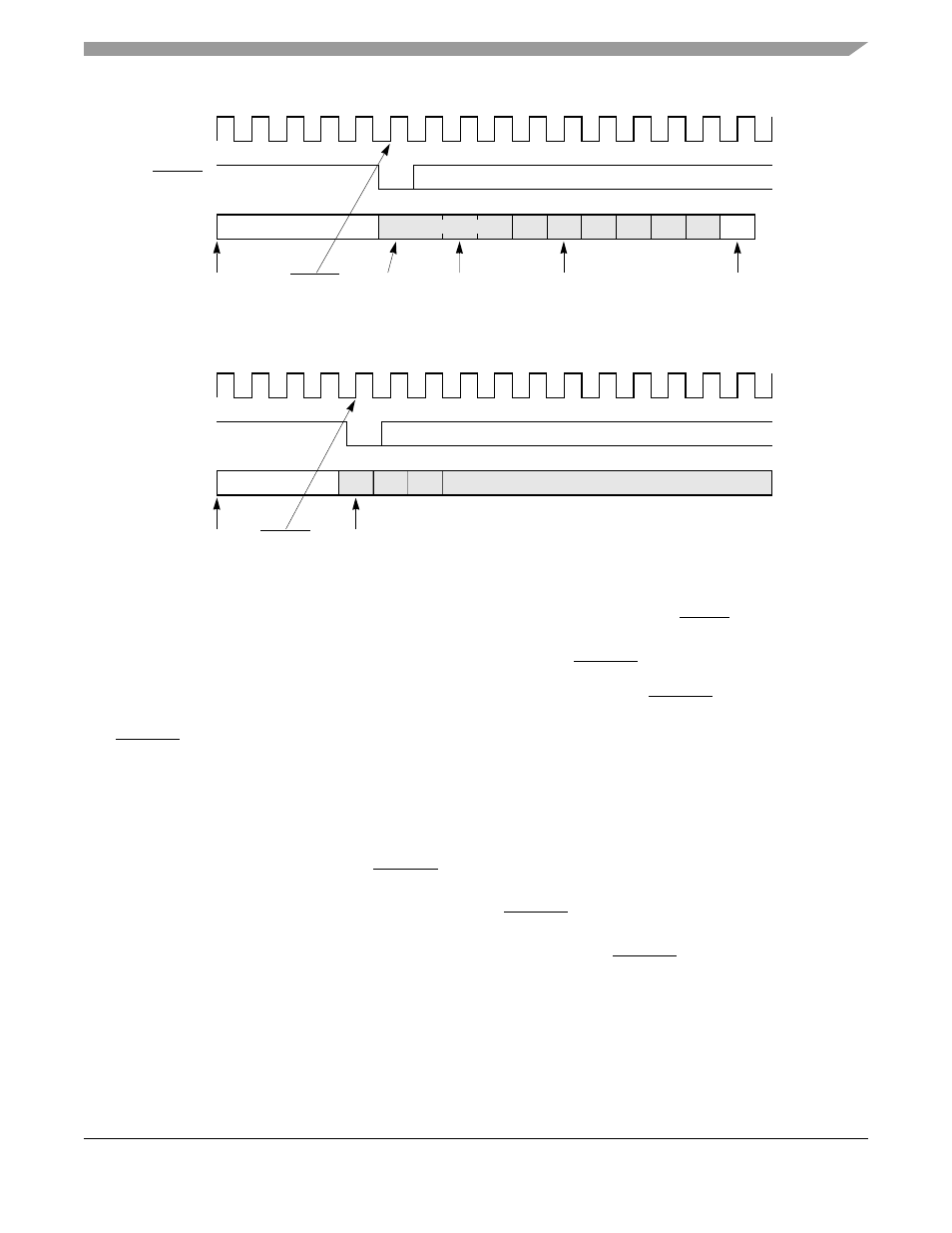

Figure 27-11. Synchronization with SMSYN

x

If both SMCMR[REN] and SMCMR[TEN] are set, the first falling edge of SMSYN causes both the

transmitter and receiver to achieve synchronization. The SMC transmitter can be disabled and reenabled

and SMSYN can be used again to resynchronize the transmitter itself.

Section 27.2.4, “Disabling SMCs

describes how to safely disable and reenable the SMC. Simply clearing and setting TEN may

be insufficient. The receiver can also be resynchronized this way.

27.4.5

Using the Time-Slot Assigner (TSA) for Synchronization

The TSA offers an alternative to using SMSYN to internally synchronize the SMC channel. This method

is similar, except that the synchronization event is the first time-slot for this SMC receiver/transmitter after

the frame sync indication rather than the falling edge of SMSYN.

Chapter 15, “Serial Interface with

describes how to configure time slots. The TSA allows the SMC receiver and

transmitter to be enabled simultaneously and synchronized separately; SMSYN does not provide this

capability.

shows synchronization using the TSA.

SMCLK

SMSYN

SMTXD

1s are sent

Five 1s are sent

TEN set

here

Tx FIFO

loaded

approximately

here

Five 1s

assume

character

length

equals 5

First bit of

first 5-bit

transmit

character

(lsb)

Transmission

could begin

here if Tx FIFO

not loaded

in time

SMSYN

detected

low here

SMCLK

SMSYN

SMRXD

REN set

here or

First bit

of receive

data

(lsb)

SMSYN

detected

low here

enter hunt

mode

command

issued

NOTES:

SMCLK is an internal clock derived from an external

CLKx or a baud rate generator.

1.

This example shows the SMC receiver and transmitter

2.

enabled separately. If the REN and TEN bits were set at

the same time, a single falling edge of SMSYN would

synchronize both.

SMC1 Transmit Data

SMC1 Receive Data