11 error control register (ecr), Figure 9-25. error control register (ecr), Error control register (ecr) -38 – Freescale Semiconductor MPC8260 User Manual

Page 344: Table 9-12 describes ecr fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-38

Freescale Semiconductor

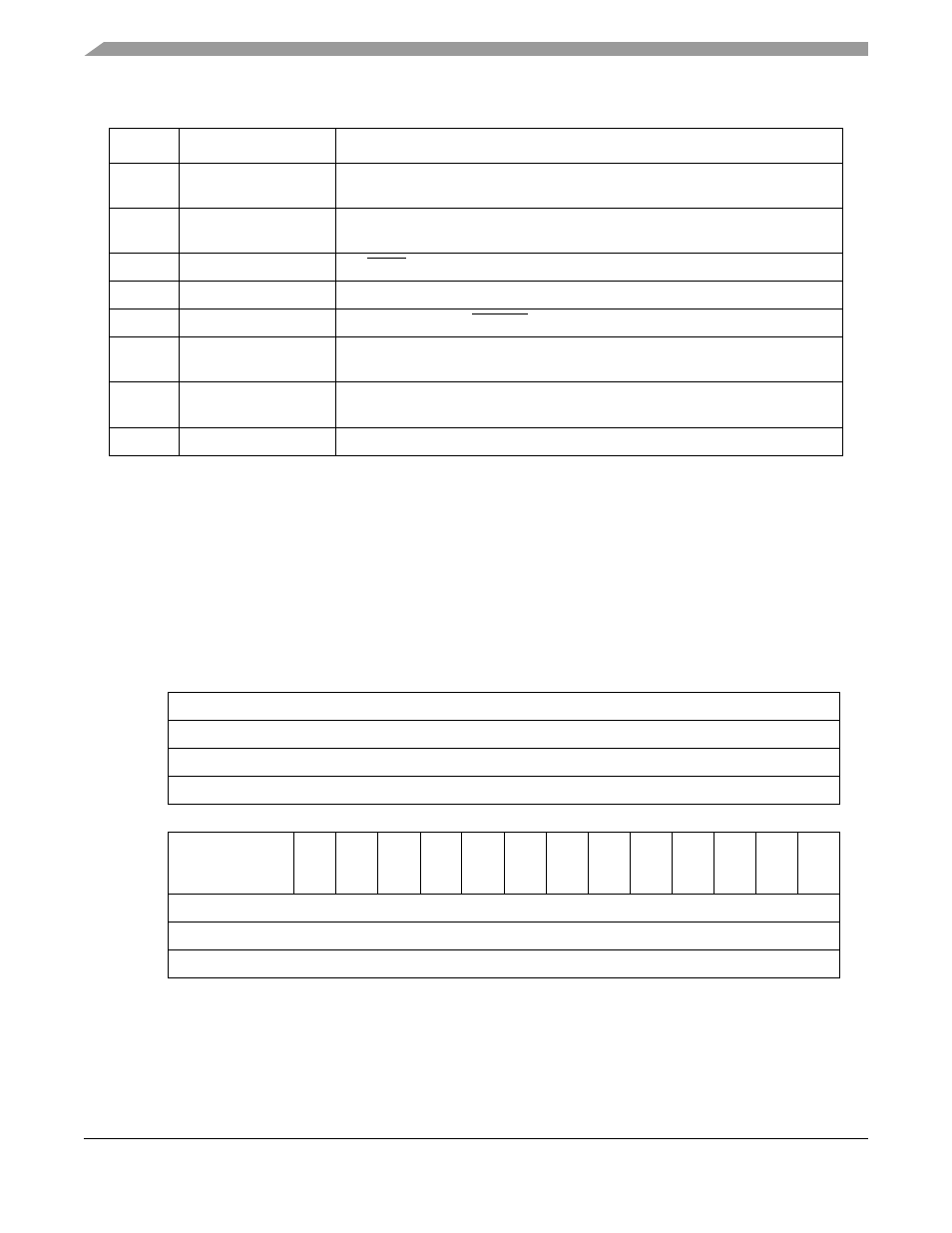

9.11.1.11 Error Control Register (ECR)

The error control register (ECR) register, shown in

, determines whether the IOU asserts an

interrupt or a machine check for the error conditions listed in

. The IOU asserts an interrupt or

machine check only if the mask bit for the error condition (refer to

) is set. Each bit is defined

as follows:

•

Zero: The IOU issues an interrupt upon the error condition.

•

One: The IOU issues a machine check upon the error condition.

Figure 9-25. Error Control Register (ECR)

describes ECR fields.

7

PCI_PERR_WR

PCI parity error received on a write. The PowerQUICC II sinks PERR. This error

is only a function of data.

6

PCI_PERR_RD

PCI parity error received on a read. The PowerQUICC II sinks PERR. This error

is only a function of data.

5

PCI_SERR

PCI SERR received.

4

PCI_TAR_ABT

PCI target abort

3

PCI_NO_RSP

PCI no response (no DEVSEL; master abort).

2

PCI_DATA_PAR_RD

PCI read data parity error. The PowerQUICC II sources PERR. This error is only

a function of data.

1

PCI_DATA_PAR_WR

PCI write data parity error. The PowerQUICC II sources PERR. This error is only

a function of data.

0

PCI_ADDR_PAR

PCI address parity error (read or write).

31

16

Field

—

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x1088E

15

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Field

—

I2O_

DBMC

NMI

IRA

I2O_

IPQO

I2O_

OFQO

PERR_

WR

PERR_

RD

SERR

TAR_

ABT

NO_

RSP

DATA_

PAR_

RD

DATA_

PAR_

WR

ADDR_

PAR

Reset

0000_0000_1111_1111

R/W

R/W

Addr

0x1088C

Table 9-11. EMR Field Descriptions (continued)

Bits

Name

Description